## **Digital System Clocking:** High-Performance and Low-Power Aspects

Vojin G. Oklobdzija, Vladimir M. Stojanovic, Dejan M. Markovic, Nikola M. Nedovic

### Chapter 5: High-Performance System Issues

al System Clocking is assuming ever greater importance as clock speed increases, doublin three years. This —the first book to focus entirely on clocked storage elements, "Flip Flaps ("acthes" — provides an in-depth introduction to the subject for both professional compute n engineers and graduate-level computer engineering students. In Dig Performance and Low-Power Aspects, you will find information on:

- a in synchronous systems including on-chip clock generation, timing pa ching in synchronous synchrony I clock signal distribution thoased and Flip-Flop system design tempatic derivation of clocked storage elements

- ming analysis

- rtainties and dynamic time bor

- circuit techniques, clock gating, and dual-edge triggering anvironment and techniques for transistor sizing

is representative microprocessor examples, including clocking for Intel<sup>®</sup>, Sun Alpha, and IBM processors, Digital Systems Clocking: High-Performance and icts provides much-needed answers about a technology that stands as a cente

OJIN G. OKLOBDZUJA is an IEEE Fellow and Distinguished lecturer. He has been a con bant for major computer and electronics companies in the fields of high-parformance sys ms, low-power design, and VISI arithmetic. He is the holder of fourteen patents on computer sign and has published extensively on the subject. Dr. Oklobdzija worked at the IBM TJ earch Center, where he did pioneering work on RISC architecture and machine t starting with the IBM 801. He received his PhD from the University of Californic , in 1982. Currently he is a professor of Electrical and Computer Enginee ity of California at Davis, where he directs the Advanced C a Laboratory (ACSEL)

VLADIMIR M. STOJANOVIC is a PhD candidate in the VLSI group, Electrical Engineering Department, Stanford University, and a design engineer at RAMBUS Corp. He obtained the MSEE degree from Stanford University and the Dipl. Ing. degree in Electrical Engineering from the University of Belgrade, Yagalatvia. He was a research scholar at ACSEL.

A. MARKOVIC is a PhD candidate and a member of the Berkeley Wireless Researc It makes on a ciril conduction and memory of me personal versions, whereas a second the Department of Electrical Engineering and Computer Science, University of of Barkeley. He received the MSEE degree from UC Barkeley and the Dipl. Ing m the School of Electrical Engineering, University of Belgrade, Yugoslavia. Mr received the 2000–2001 UC Barkeley CaNTEW Fellow Award for excellence in teaching of industry engineers. He is a current member of the UC Berkeley Hitachi Fellow Te He was a research scholar at ACSEL.

NIKOLA NEDOVIC is a research staff member at Fujitu America Laboratories working on high-speed digital circuits. He is currently completing his PhD as a member of the ACSEL group at the University of California. He is an Electrical Engineering graduate from the University of

#### IEEE IEEE PRESS

Visit www.wiler.com/electrical WILEY-INTERSCIENCE

## **Digital System** Clocking

High-Performance and Low-Power Aspects

Vojin G. Oklobdzija, Vladimir M. Stojanovic, Dejan M. Markovic, and Nikola Nedovic

#### Wiley-Interscience and IEEE Press, January 2003

# Absorbing Clock Uncertainties

- Clock uncertainties

- Clock skew

- Clock jitter

- Trends:

- Clock distribution becomes progressively difficult due to:

- load mismatch

- Process, voltage, and temperature variations.

- The clock uncertainties occupy increasing portion of the cycle time; typically 2 FO4.

- The ability to reduce impact of these uncertainties is one of the most important properties of the high-performance system.

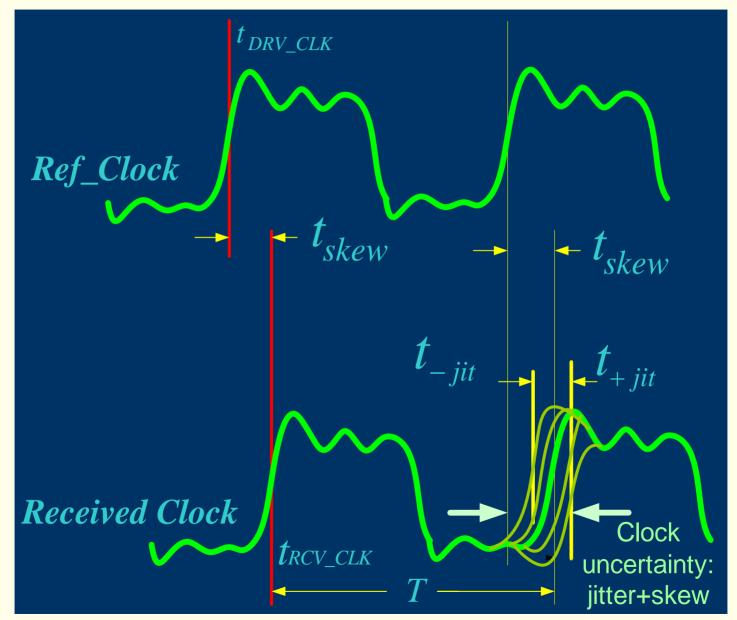

### Clock Generation and Distribution Non-idealities

- Jitter

- Temporal variation of the clock signal manifested as uncertainty of **consecutive** edges of a periodic clock signal.

- It is caused by *temporal* noise events

- Manifested as:

- cycle-to-cycle or short-term jitter,  $t_{JS}$

- long-term jitter,  $t_{JL}$

- Mainly characteristic of clock generation system

- Skew

- Time difference between temporally-equivalent or concurrent edges of two periodic signals

- Caused by *spatial* variations in signal propagation

- Manifests as CSE-to-CSE fluctuation of clock arrival at the same time instance

- Characteristic of clock distribution system

# Clock Uncertainties

Nov. 14, 2003

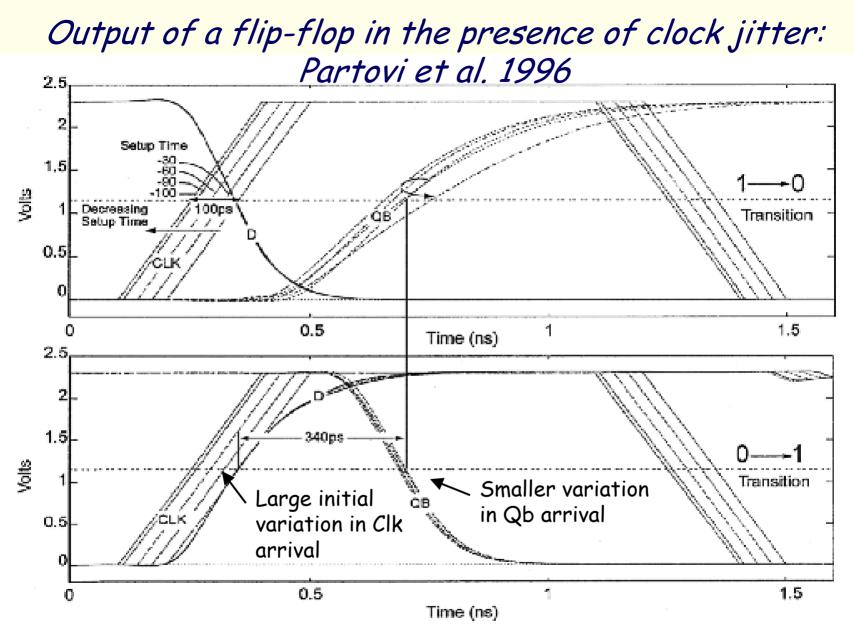

## Clock Uncertainty Absorption Using Soft Clock Edge

A recent design of a Flip-Flop, controlled by a narrow, locally generated clock pulse, with negative Setup Time exhibits some degree of clock uncertainty absorption.

Nov. 14, 2003

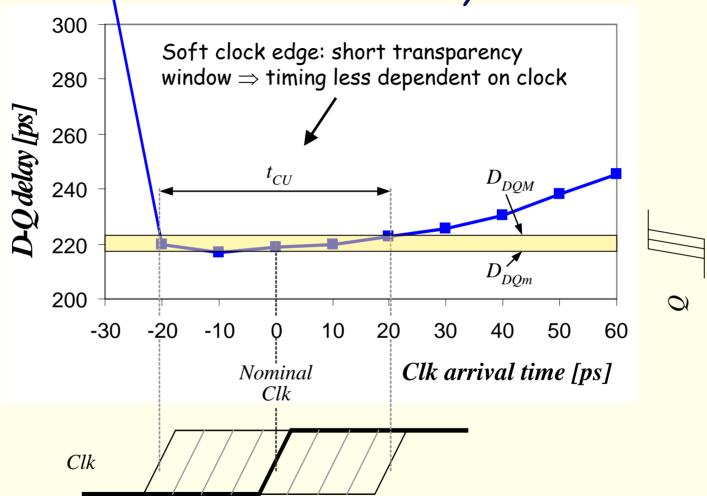

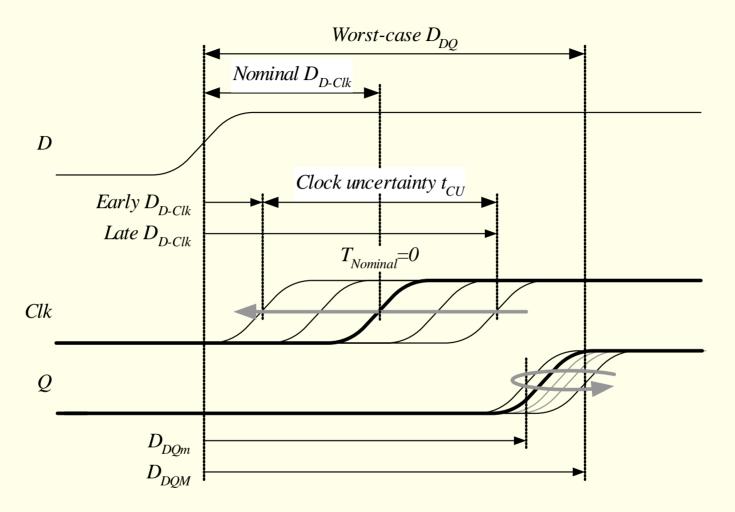

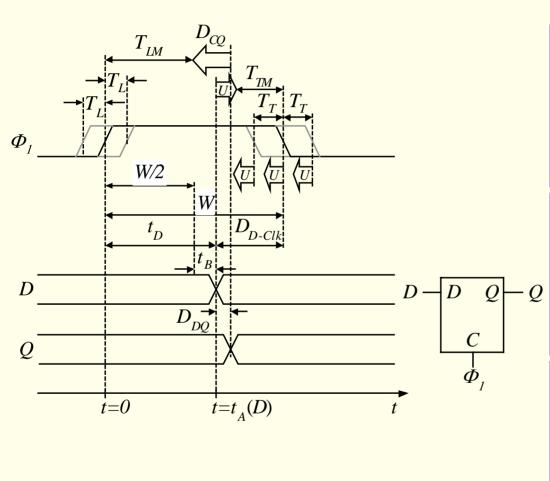

### Data-to-output characteristics in the presence of clock uncertainty

Data-to-Output Delay versus Clock Arrival Time when the data arrival time is constant. When no clock uncertainties are present, the clock is scheduled to arrive so that D-Q delay ( $t_{DQm}$ ) is smallest, in order to minimize the CSE overhead. Nov. 14, 2003 Digital System Clocking: Oklobdzija, Stojanovic, Markovic, Nedovic

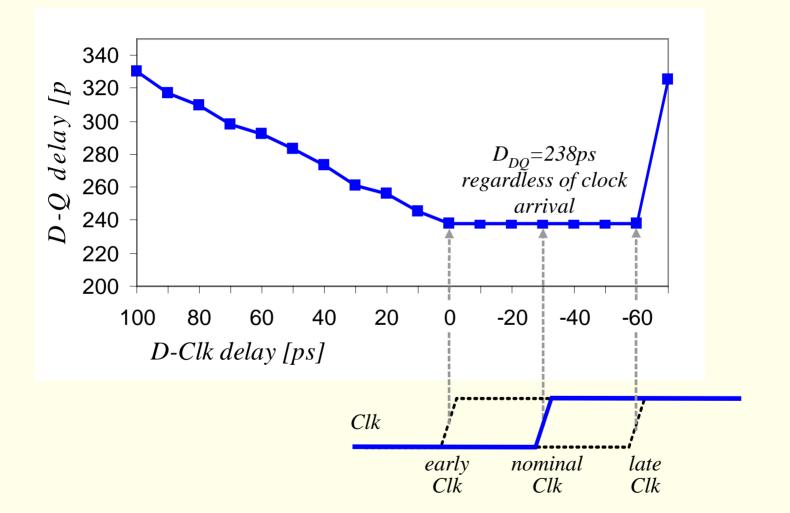

### Dependence of data-to-output delay on clock arrival

The key role of a CSE is to minimize the propagation of clock uncertainty to the CSE output:

$$D_{DQM} = \max_{t} [D_{DQ}(U_{Opt} + t)], t \in [-t_{CU}/2, t_{CU}/2]$$

Nov. 14, 2003

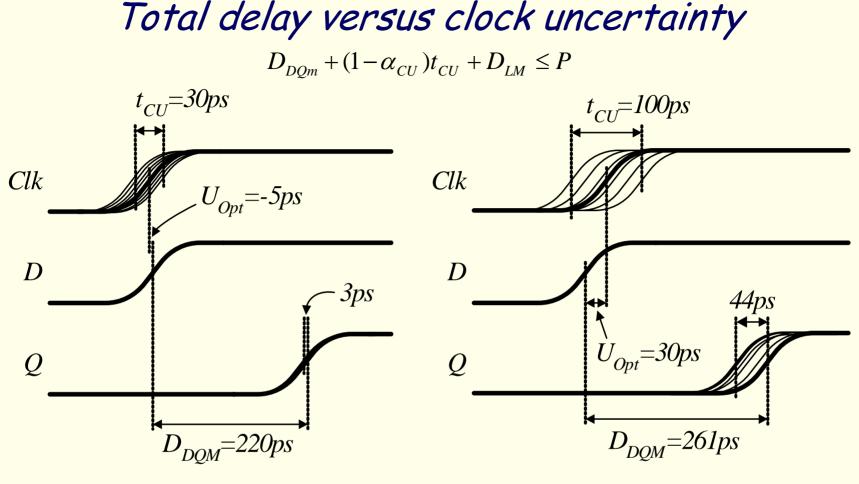

## Timing Analysis with Clock Uncertainty Absorption

(**a**)  $t_{CU} = 30 ps \ (a_{CU} = 90\%)$  (**b**)  $t_{CU} = 100 ps \ (a_{CU} = 56\%)$

We formulate *clock uncertainty absorption*  $\alpha_{CU}$  of a storage element as the portion of the total clock uncertainty not reflected at the output:

$$\alpha_{CU} = \frac{t_{CU} - (D_{DQM} - D_{DQm})}{t_{CU}} = 1 - \frac{\Delta D_{DQ}}{t_{CU}}$$

Nov. 14, 2003

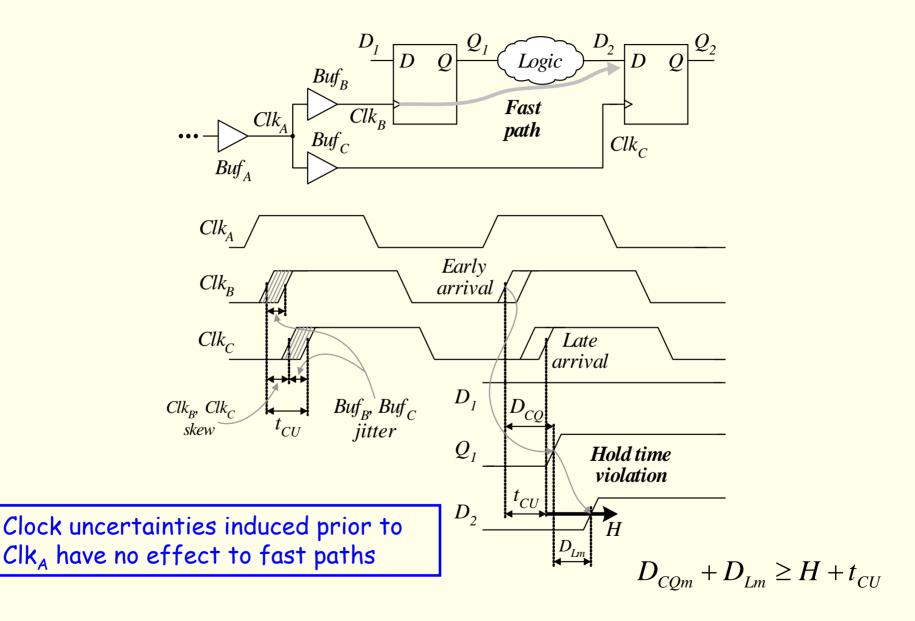

### Critical race in the presence of clock uncertainty

Nov. 14, 2003

### Idealized D-Q delay characteristic as a function of clock arrival

Nov. 14, 2003

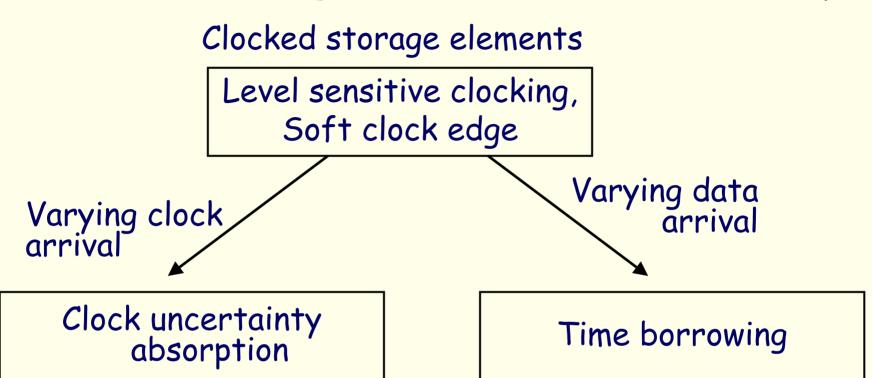

## Time Borrowing

## Time Borrowing

Classification:

- Dynamic time borrowing

- Scheduling data to arrive to CSE when CSE is transparent

- No "hard" boundaries between stages

- Occurs in latch-based level sensitive and soft-edge clocking.

- Static time borrowing

- Inserting delay between clock inputs of the clocked storage elements.

- Clocks are scheduled to arrive so that the slower paths obtain more time to evaluate, taking away the time from faster paths.

- It can operate with conventional hard-edge Flip-Flops.

- Also called opportunistic skew scheduling

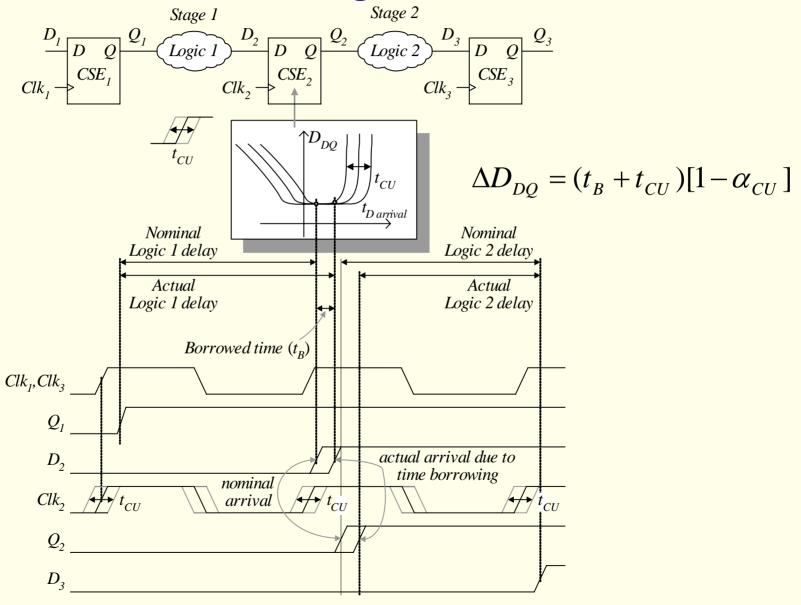

## Dynamic Time Borrowing

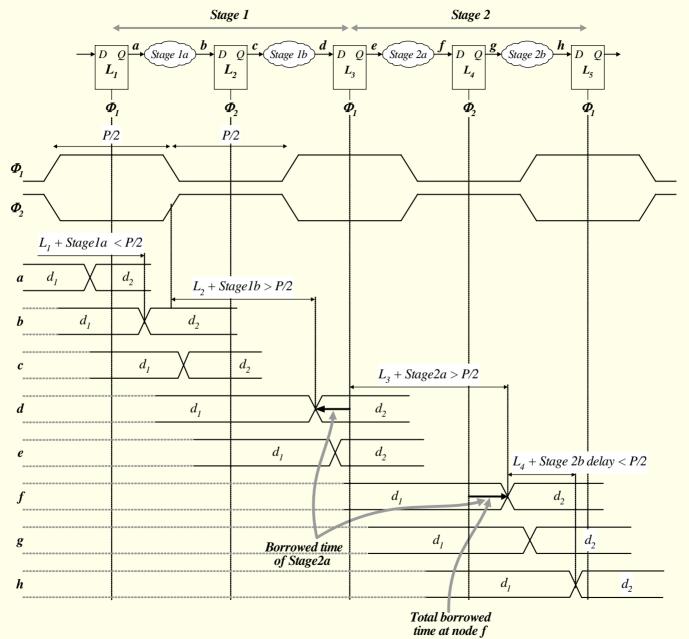

#### Timing of two-phase level-sensitive pipeline with time borrowing

Nov. 14, 2003

#### Timing Analysis with Time Borrowing: Late Data Arrival

The minimum clock cycle time of the pipeline is not determined by the delay of the slowest stage in the pipeline. It is rather the average delay of the logic and latches through all stages.

$$P = \frac{1}{N} \sum_{i=1}^{2N} (D_{DQ,i} + D_{Logic,i})$$

Assumptions:

1) all logic blocks are used in time borrowing, 2) after N stages, the pipeline produces data at the same point in the cycle at which the input data was acquired

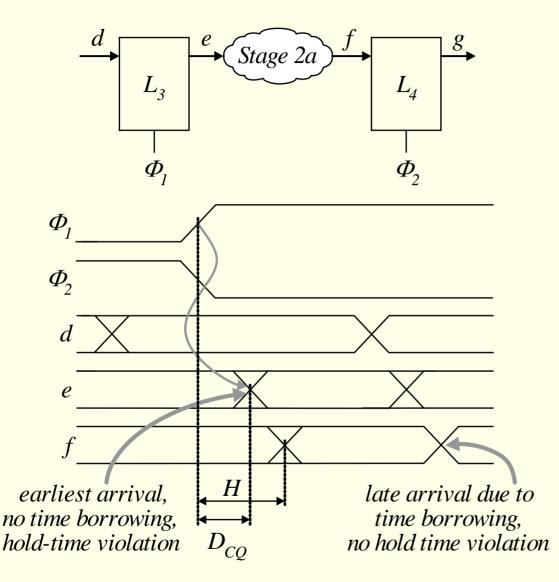

### Fast-path hazard

In fast paths, analysis must assume that the data arrives at earliest possible time -> disregard effects of time borrowing

### Time borrowing and signal loops

The timing of signals in the loops, should be treated separately.

If the overall propagation delay through the loop occur later with each cycle, it will result in a Setup Time violation.

Any signal loop that borrows time from itself will eventually cause a timing violation.

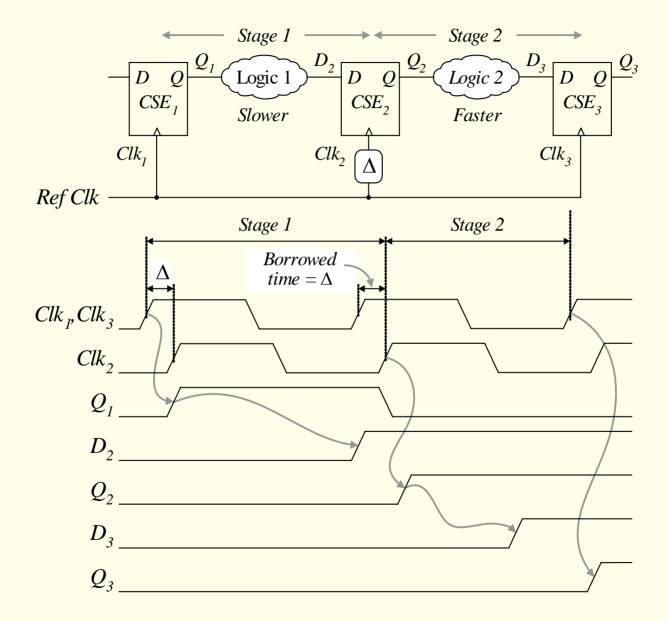

# Static Time Borrowing (Opportunistic Skew Scheduling)

### Opportunistic skew scheduling

Nov. 14, 2003

## Opportunistic skew scheduling

<u>Advantages:</u>

- It can operate with conventional Flip-Flops.

- It places fewer constraints onto the circuit design, allowing additional time slack where necessary.

- ⇒ useful in localized critical paths where every improvement directly increases the system clock rate

### Disadvantages:

- It increases the complexity of the clock distribution system.

- It is hard to control the inserted delays over process, supply and temperature variations.

- The analysis of clock skew is also complicated in this asymmetric clock distribution network.

- $\Rightarrow$  impractical on a large-scale level

## Time Borrowing and Clock Uncertainty

#### Clock uncertainty absorption and time borrowing exploit the same data transparency property of CSE

Nov. 14, 2003 Digital Sys

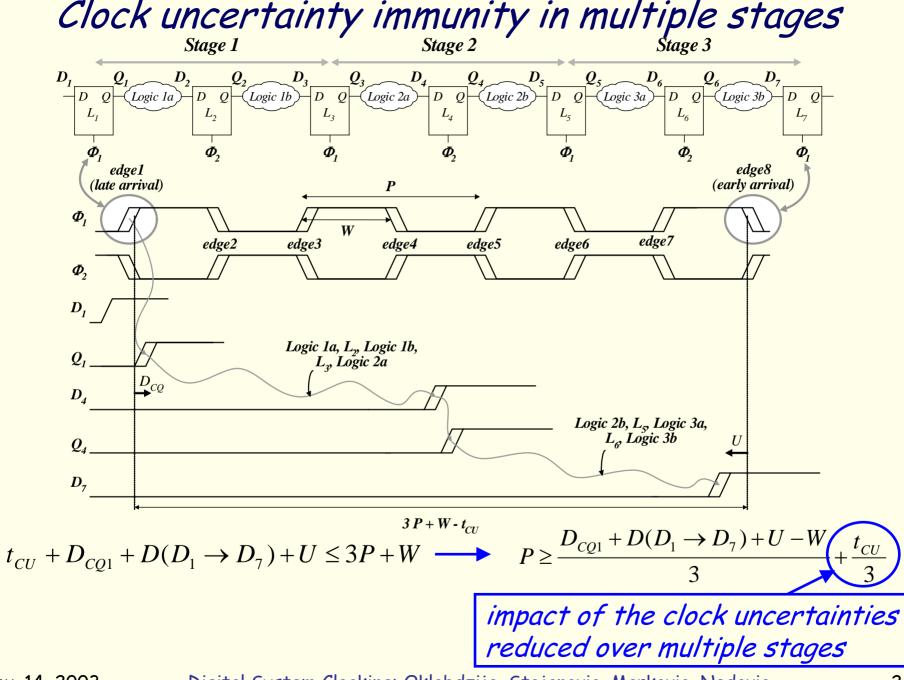

## Clock Uncertainty Absorption with Level-Sensitive Clocking

### Clock uncertainty immunity in single stage

System tolerates up to  $T_{L,\Phi_1} + T_{T,\Phi_2} \leq D_{CQm} + D_{Lm} - V - H$ before violating hold time System tolerates up to  $T_T \leq W / 2 - t_B - U$ before violating setup time System tolerates up to  $T_{L} \leq t_{B} + D_{DQ} - D_{CQ} + W/2$ to keep borrowing time

Nov. 14, 2003

Nov. 14, 2003

## Summary: Effects of clock uncertainties to a system with level-sensitive clocking

- Decreasing of the margins for time borrowing.

- The pipeline absorbs the uncertainties for the data that arrives during the transparency period of the Latch.

- The effect of the uncertainties is reduced to an average uncertainty over all stages in the path.

# Soft-Edge Sensitive Clocking

### Time borrowing with uncertainty-absorbing clocked storage elements

Nov. 14, 2003

# Conclusion

- High-performance CSE requirements:

- Speed

- Clock uncertainty absorption  $\Rightarrow$  to accommodate increasing effect of clock skew and jitter

- Time borrowing  $\Rightarrow$  to eliminate effects of imbalanced stage delays

- Essential circuit technique: eliminate hard edges in critical paths

- Flip-flops with soft clock edge, level-sensitive latches become preferred choice of CSE

- Clock uncertainty absorption capability can be traded for time borrowing