ı col ıe re

iplier that may pass ed by

ed. If most zero on of t left

that  $\xi = \overline{1}$ . it in-This I has same sub-

than ative acter

ected serve os or ed, it im-

ts to but or to will ever

rof. ince rote date

Sci., e det. of ne 1,

iois.

division and multiplier recoding procedures," Dept. of Computer Sci., University of Illinois, Urbana, Rept. 252, December 1967.

5] J. O. Penhollow, "A study of arithmetic recoding with applications to multiplication and division," Dept. of Computer Sci., University of Illinois, Urbana, Rept. 128, September 1962.

C. S. Wallace, "Suggested design for a very fast multiplier," Dept. of Computer Sci., University of Illinois, Urbana, Rept. 133, February 11, 1963.

[7] J. E. Robertson, internal memo, February 11, 1968.

[8] —, "Methods of selection of quotient digits during digital division," Dept. of Computer Sci., University of Illinois, Urbana, File 663, 1965.

[9] D. E. Atkins, "Higher radix division using estimates of the divisor and partial remainders," *IEEE Trans. Computers*, vol. C-17, pp. 925-934, October 1968.

[10] ——, "Illiac III computer system manual: Arithmetic units," vol. 1, Dept. of Computer Sci., University of Illinois, Urbana, Rept. 366, December 1969.

# A Universal Arithmetic Building Element (ABE) and Design Methods for Arithmetic Processors

ALGIRDAS AVIŽIENIS, MEMBER, IEEE, AND CHIN TUNG, MEMBER, IEEE

Abstract—The advent of large-scale integration of logic circuits requires the definition of digital computer structure in terms of large functional arrays of logic of very few types. This paper describes a single-package arithmetic processor called the arithmetic building element (ABE). The ABE accepts operands in either conventional or signed-digit radix-r representation and produces signed-digit results, which the ABE can reconvert to conventional form. Radix 16 is chosen for illustrations. Arrays of ABE's may be arranged to implement unittime parallel addition, all-combinational multiplication, and more complex functions which are presently computed by subroutines. To facilitate such arithmetic design, a graph model is developed which permits a translation of the given arithmetical algorithm into an interconnection diagram of ABE's. The design procedure is illustrated by an array for polynomial evaluation. Speed, cost, and roundoff error of the array are considered. A computer program has been written for the automatic translation of the algorithm graph to an interconnection graph, and for the evaluation of the cost and speed for a given polynomial degree and a given precision requirement.

Index Terms—Arithmetic array modeling, arithmetic building element, arithmetic processors, computer-aided processor design, graph models of arithmetic, microelectronic building block, polynomial evaluation array, signed-digit number systems.

#### I. INTRODUCTION

HE ADVENT of large-scale integration in the manufacturing of logic circuits has created a new challenge to the designers of digital systems. In order to take advantage of the potentially low cost per circuit it is necessary to define large functional packages of logic elements which

Manuscript received December 15, 1969; revised March 13, 1970. This research was sponsored by Atomic Energy Commission Contract AT(11-1) Gen 10 Project 14.

A. Avižienis is with the Department of Computer Science, University of California, Los Angeles, Calif. 90024.

C. Tung was with the Department of Computer Science, University of California, Los Angeles, Calif. He is now with the IBM Research Laboratory, San Jose, Calif. 95114.

have multiple usage in various systems [13]. Storage arrays are most directly suitable for such implementation because of their repetitive internal structure. A typical large arithmetic processor from current generation computers is not readily built up from sizable identical subsystems. To a large extent this is due to the need for a logic structure which provides fast carry propagation during addition. Either the addition time or the structure varies with varying operand lengths.

An algorithm for a carry-free addition and subtraction in which the addition/subtraction time remains independent of the length of the operands has been devised for redundant signed-digit (SD) number representations [1]. SD representations are redundant positional representations with a constant integer radix  $r \ge 3$ , in which the allowed digit values are a sequence of 2a+1 integers:

$$\{\bar{a}, \dots, \bar{1}, 0, 1, \dots, a\}$$

, with  $r/2 < a < r$ .

In this paper the overbar  $(\overline{1}, \overline{3}, \text{etc.})$  is used to designate negative digit values.

Further studies of SD number systems have shown that the redundancy of representation allows other unusual algorithms, such as wired-in significant-digit arithmetic [2], [14], most-significant-digit-first serial addition and multiplication [2], algorithms which can accept both SD and conventional operands to produce SD results [3], and two-digit product as well as multidigit sum algorithms whose results are suitable inputs to the carry-free two-digit sum algorithm [4]. The self-contained digit-by-digit nature of these algorithms suggested the possibility of a general arithmetic building block suitable for microelectronic implementation [4], [5], [7]. This paper presents the results of

recent investigations which have led to the definition of a single universal arithmetic building element (ABE). The ABE incorporates all the desirable properties of SD arithmetic enumerated above as well as the means to accept conventional number inputs and to convert SD numbers back to conventional form. A storage register at the ABE output provides for "pipelining" [12] of ABE arrays, with the resulting increase in the effective rate of computing. A single ABE can serve as the entire arithmetic unit of a digit-serial computer.

A second important feature of the ABE approach is the separation of the functions of logic design and arithmetic design. The ABE is specified entirely by the numeric algorithms which express the values of output digits in terms of the input digits. These algorithms are called the transfer algorithms of the ABE. The logic design aspect is restricted to the internal realization of the transfer algorithm within the ABE. It will depend on the choice of the radix and of the encoding of digit values. The arithmetic design is the specification of ABE arrays for a given algorithm, which may range from addition of two operands to matrix inversion and to the evaluation of trigonometric, logarithmic, and similar functions [6], [7]. The arithmetic design is accomplished by a systematic procedure which is described in this paper. The arithmetic algorithm is expressed by a directed graph model which is translatable to an interconnection diagram for ABE's.

The procedure of arithmetic design is illustrated by the example of an ABE array for polynomial evaluation. A minimally redundant radix-16 SD number system ( $\overline{9}$  to 9) is chosen for the specific illustrations [4]. The practical choice of radices for an ABE is limited to radix 10 and radices  $2^k$  with  $k \ge 2$ . Radix 10 requires only 13 digit values ( $\overline{6}$  to 6); thus storage requirements are not increased compared to the conventional form (0 to 9). Radices  $2^k$  (i.e., 4, 8, 16, 32, etc.) require one additional bit of storage per digit when immediate reconversion is not performed. Their advantages are their compatibility with conventional binary input operands. Further, full utilization of available internal logic complexity is possible by choosing the largest acceptable value of k in  $r=2^k$ .

The choice of a specific radix is not necessary in the following description of the ABE transfer algorithms as long as the details of internal logic design are avoided.

# II. THE ARITHMETIC BUILDING ELEMENT (ABE)

A set of five arithmetic building blocks called arithmetic microsystems was described in 1966 [4]. These building blocks employed SD number systems, and the examples were implemented in the minimally redundant radix-16 SD system. The number of building blocks was subsequently reduced from five to two, the universal building unit (UBU) and the reconversion and sign unit (RSU) [5]. The present paper describes a single building block, called the arithmetic building element (ABE). The reduction of the set to one element is attained at the cost of greater internal complexity and reduced speed of reconversion to conventional repre-

sentation. New and more effective forms have been devised for most ABE transfer algorithms.

The ABE is implemented with combinational logic and storage elements for all output signals. The following description of the ABE presents a detailed statement of the algorithms which define its internal logic design. The description uses the following notation:

[y] floor (integer  $[y] \le y < [y] + 1$ )

[y] ceiling (integer  $[y] - 1 < y \le [y]$ )

r radix

a maximum SD digit magnitude ( $[1 + r/2] \le a \le r - 1$ )

[- (overbar) additive inverse

Arithmetic

Operations: + addition

- subtraction

× (or adjacency) multiplication

/ division

Logic

Operations:

| V OR |

| NOR |

| AND |

| NAND |

| NOT |

| EXCLUSIVE OR .

#### A. External Structure of the ABE

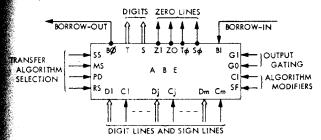

The external connections of the radix-r ABE are shown in Fig. 1. The *inputs* supply either control or data signals. There are four types of *control inputs* (individual logic variables):

- 1) Four Algorithm Lines: SS (simple sum), MS (multiple sum), PD (Product), and RS (Reconversion). One of these four lines is permanently set to the value 1 and determines the arithmetic transfer algorithm of the ABE.

- 2) Two Algorithm-Modifier Lines: CI (conventional input), and SF (significance arithmetic). When either one or both of these are set to the value 1, they modify the algorithm according to their specifications.

- 3) Two Output-Gating Lines: G1 and G0. The outputs of the ABE are held to zero by the logic condition  $\sim G0 \vee G1 = 0$ ; otherwise the specified outputs are available

- 4) m Sign Lines: C1,  $\cdots$ , Cj,  $\cdots$ , Cm, with  $m \le r + 1$ . The logic value 1 on the sign line Cj commands a change of sign (additive inverse algorithm) for the input digit appearing on the associated input digit line Dj. The sign change occurs before the algorithm is applied to the input digit.

The remaining input lines are data inputs.

- 5) m Digit Lines: D1,  $\cdots$ , Dj,  $\cdots$ , Dm, with  $m \le r + 1$ . Each digit line is a bundle of d bit lines. The d logic variables applied on one digit line represent the value of one radix-r input digit. The value of d depends on r and on the choice of encoding.

- 6) One Borrow-In Line: BI. This input is used to represent an incoming borrow for the reconversion (RS) from SD to conventional form.

Fig. 1. Input and output lines of the arithmetic building element.

The *outputs* of the ABE represent the results computed the specified algorithm. Two outputs (T and S represent gits; all others are individual logic variables. The followoutputs are provided.

- 1) Two Output-Digit Lines: T and S. They represent the cits of the result and are also bundles of d bit lines each.

- 2) Two Zero Lines: Z1 and Z0. The line Z1 assumes the gic value 1 only if the result computed by the ABE has e numeric value zero. The line Z0 assumes the logic value Z1.

- 3) Two Zero-Significance Lines:  $T\phi$  and  $S\phi$ . They assume logic values 1 only if the input SD digits for the recontrol (RS) algorithm are nonsignificant ("space") zeros.

- 4) One Borrow-Out Line: BQ. It is related to the BI input ne and represents an outgoing borrow in the reconversion neorithm.

Additional and more specific discussion of the inputs and utputs will be found in the subsequent discussion of the BE algorithms and their modifiers.

Our example employs r=16 with minimal redundancy a=9). One digit line  $D_j$  receives five logic variables which epresent the 19 digit values  $\overline{9}$  to 9 inclusive. The maximum flowable number of digit lines is m=17.

#### **B**. Number Formats

Input operands and output results are positional, constant radix-r number forms:

$$x^1 = x_{-n}^1 \cdots x_{-1}^1 x_0^1 x_1^1 x_2^1 \cdots x_i^1 \cdots x_n^1$$

Bither conventional (CONV) or signed-digit (SD) forms are employed. The allowed values of a digit  $x_i^1$  are  $\{0, 1, \dots, r-1\}$  for CONV forms, and  $\{\bar{a}, \dots, \bar{1}, 0, 1, \dots, a\}$  for SD forms, with the constraint r/2 < a < r. Unless explicitly otherwise specified, SD forms with minimal redundancy  $(a = \lfloor 1 + r/2 \rfloor)$  are assumed.

Rightward indexing of digits is used unless otherwise stated:

$$i = \dots, -n, -(n-1), \dots, -2, -1, 0, 1, 2, \dots, n, \dots$$

With this indexing convention, greater indices refer to less significant digit positions. Positive indices are used to indicate positions to the right of the radix point, while negative and zero indices identify digit positions to the left of the radix point.

When more than one operand is considered, the superscript is employed to identify a specific operand, i.e.,  $x^1$  and

$x^2$  for two operands, or  $x^1, x^2, \dots, x^j, \dots, x^m$  for m operands. The *i*th digit of  $x^j$  is uniquely identified as  $x^j$ .

# C. The Additive-Inverse Algorithm (Cj = I)

A sign line Cj is associated with every digit line Dj in the ABE (Fig. 1). When the digit  $x_i^j$  is the input on Dj, an associated sign-change variable  $c_i^j$  is applied on Cj. The logic value  $c_i^j = 1$  causes the sign of the digit  $x_i^j$  to be changed (except when  $x_i^j$  is zero) to the opposite value before the selected ABE algorithm is applied to the input digits.

The sign-change variables  $c_i^j$  permit the specification of either the operand  $x^j$  or its additive inverse  $-x^j$  as the input for any algorithm which is implemented by ABE's. For example, the simple-sum algorithm can form any one of the four sums:

$$x^{1} + x^{2}$$

;  $(-x^{1}) + x^{2}$ ;  $x^{1} + (-x^{2})$ ;  $(-x^{1}) + (-x^{2})$

with appropriate application of the sign-change variables.

In the following discussion of the ABE algorithms the effect of  $c_i^j$  will be expressed in terms of the *arithmetic sign* variable  $\sigma_i^j$  which is defined as

$$\sigma_i^j \equiv (\sim c_i^j - c_i^j)$$

and assumes the values +1 and -1. The value of the modified input digit which is processed by the ABE algorithm is the product  $\sigma_i^j x_i^j$ . Unless explicitly otherwise stated, the same value of  $c^j$  is specified for the entire operand  $x^j$ . The value of an input operand is given as  $\sigma^j x^j$  in the subsequent discussion, where  $\sigma^j$  is the *common sign* variable for the operand.

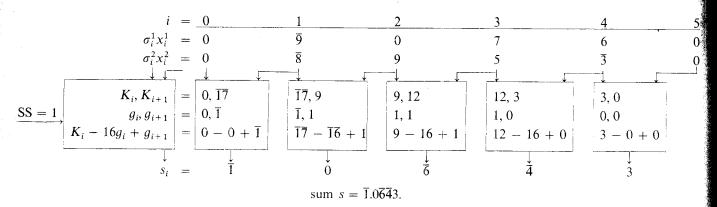

#### D. The Simple-Sum Algorithm (SS = 1)

The SS algorithm computes one SD sum digit  $s_i$  for the n+1-digit-long sum  $s=\sigma^1x^1+\sigma^2x^2$  of two n-digit SD operands.

- I) Inputs:  $x_i^1$ ,  $x_{i+1}^1$ ,  $x_i^2$ ,  $x_{i+1}^2$  on D1, D2, D3, D4, respectively;  $c^1$  on C1 and C2;  $c^2$  on C3 and C4.

- 2) Outputs: Sum digit  $s_i$  on S; zero-condition  $z_i$ ,  $\sim z_i$  on Z1, Z0, respectively  $(z_i = 1 \text{ if } s_i = 0)$ .

- 3) Algorithm: Define the digit sum  $K_h$  (for h=i and h=i+1) as

$$\sigma_h^1 x_h^1 + \sigma_h^2 x_h^2 \equiv K_h.$$

Compute (for radix  $r \ge 3$ ) the output digit  $s_i$  as follows:

$$s_i = K_i - rg_i + g_{i+1}$$

where

$$g_h = \begin{cases} 0, & |K_h| < a \\ 1, & K_h \ge a \\ \overline{1}, & K_h \le \overline{a}. \end{cases}$$

The operands  $x^1$  and  $x^2$  are extended by prefixing one zero digit at the left end of each. This extension is required to assure the correct n+1 digit sum s. A total of n+1 ABE's is used.

4) Example (r = 16, a = 9):  $c^1 = c^2 = 0$ ;  $x^1 = 0.\overline{9}076$ ;  $x^2 = 0.\overline{8}95\overline{3}$  (internal values shown in decimal).

E. The Multiple-Sum Algorithm (MS = 1)

The MS algorithm computes two SD digits  $s_i$  and  $t_{i-1}$ : one each for two *n*-digit words (s, t) which represent the sum of *m* words (*n*-digit SD operands)  $x^1$  to  $x^m$  such that

$$s + t = \sum_{j=1}^{m} \sigma^{j} x^{j}$$

, with  $m \le r + 1$ .

- 1) Inputs:  $x_i^j$  on  $D_j$  and  $c^j$  on  $C_j$  for  $j = 1, \dots, m$ .

- 2) Outputs:  $s_i$  on S and  $t_{i-1}$  on T; zero-condition variables  $z_i$ ,  $\sim z_i$  for the digit sum  $\Sigma_i$  (see below) on Z1, Z0.

- 3) Algorithm: Define the digit sum  $\Sigma_i$  and its functions (for the radix  $r \ge 3$ ) as follows:

$$\Sigma_i \equiv \sum_{j=1}^m \sigma_i^j x_i^j$$

$I(\Sigma_i) = \text{integer quotient } |\Sigma_i|/r$

$R(\Sigma_i)$  = integer remainder  $|\Sigma_i| - rI(\Sigma_i)$ .

The output digits are computed as follows:

$$\operatorname{sign}(t_{i-1}) = \operatorname{sign}(\Sigma_i)$$

$$|t_{i-1}| = \begin{cases} I(\Sigma_i) + 1, & R(\Sigma_i) > a \\ I(\Sigma_i), & R(\Sigma_i) \le a \end{cases}$$

$$s_i = \Sigma_i - rt_{i-1}.$$

The constraint  $m \le r+1$  assures that the output digits  $s_i$  and  $t_{i-1}$  do not exceed the allowed range of values of the input digits  $x_i^j$ . A total of n ABE's is used.

4) Example (r = 16, a = 9):  $c^1 = c^2 = c^3 = c^4 = 0$ ;  $x^1 = 0.9\overline{8}07$ ;  $x^2 = 0.0\overline{7}\overline{5}9$ ;  $x^3 = 0.6\overline{2}\overline{4}8$ ;  $x^4 = 0.\overline{1}\overline{9}09$  (internal values shown in decimal).

$$i = 0 \quad 1 \quad 2 \quad 3 \quad 4$$

$$\sigma_{i}^{1}x_{i}^{1} = 9 \quad \overline{8} \quad 0 \quad 7$$

$$\sigma_{i}^{2}x_{i}^{2} = 0 \quad \overline{7} \quad \overline{5} \quad 9$$

$$\sigma_{i}^{3}x_{i}^{3} = 6 \quad \overline{2} \quad \overline{4} \quad 8$$

$$\sigma_{i}^{4}x_{i}^{4} = \overline{1} \quad \overline{9} \quad 0 \quad 9$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \downarrow \qquad \downarrow \qquad \downarrow$$

$$\Sigma_{i} = 1 \quad \overline{2} \quad 0 \quad 2$$

$$MS = 1 \quad \overline{14} \quad 10 \quad 9 \quad 1$$

$$t_{i} = 1 \quad \overline{2} \quad 0 \quad 2$$

sum  $(s; t) = (0.\overline{2}6\overline{9}1; 1.\overline{2}02).$

# F. The Product Algorithm (PD = 1)

The PD algorithm computes one SD product digit  $s_{k+i}^k$  for the n+1-digit-long product  $s^k = \sigma_k^1 x_k^1 \sigma^2 x^2$  of one SD digit  $x_k^1$  and the n-digit SD operand  $x^2$ .

- 1) Inputs:  $x_k^1$  on D1;  $x_i^2$ ,  $x_{i+1}^2$ ,  $x_{i+2}^2$  on D2, D3, D4;  $c^1$  on C1;  $c^2$  on C2, C3, C4.

- 2) Outputs: Product digit  $s_{k+i}^k$  on S; zero-condition variables  $z_{k+i}^k \sim z_{k+i}^k$  (for  $s_{k+i}^k$ ) on Z1, Z0.

- 3) Algorithm. Define three digit products  $\pi_{k+h}$  (for h=i, i+1, i+2) as follows:

$$\pi_{k+h} \equiv (\sigma_k^1 x_k^1) \times (\sigma_k^2 x_k^2).$$

Compute the output digit  $s_{k+i}^k$  in two steps. First, apply the MS algorithm to each  $\pi_{k+h}$  (substituting  $\pi_{k+h}$  for  $\Sigma_i$ ,  $u_{k+h-1}$  for  $t_{i-1}$ , and  $v_{k+h}$  for  $s_i$ ) to get the digits  $u_{k+h-1}$  and  $v_{k+h}$  such that

$$\begin{split} \pi_{k+i} &= ru_{k+i-1} + v_{k+i} \\ \pi_{k+i+1} &= ru_{k+i} + v_{k+i+1} \\ \pi_{k+i+2} &= ru_{k+i+1} + v_{k+i+2}. \end{split}$$

Second, perform the SS algorithm (substituting  $v_{k+i}$ ,  $v_{k+i+1}$  for  $x_i^1$ ,  $x_{i+1}^1$ , and  $u_{k+i}$ ,  $u_{k+i+1}$  for  $x_i^2$ ,  $x_{i+1}^2$ ) to get the product digit:

$$s_{k+i}^k = v_{k+i} + u_{k+i} - rg_{k+i} + g_{k+i+1}.$$

The *n*-digit operand  $x^2$  is extended by prefixing one zero digit at its left end in order to yield the correct n+1 digit product. ABE count is n+1.

When the multiplier  $x^1$  consists of more than one digit (say, g digits) we can simultaneously obtain all products  $s^k = x_k^1 x^2$  ( $k = 1, 2, \dots, g$ ). The product  $x^1 x^2$  is computed by summing the columns of product digits with the same index, using the MS algorithm followed by the SS algorithm. The total number of ABE's required to form the product  $x_k^1 x^2$  is gn + g; therefore g < n is the preferred choice when  $g \ne n$ . The maximum number of digits with the same index to be summed by the MS algorithm is  $f = \min(g, n+1)$ .

It is noted that the PD algorithm is internally more complex than the previously described product (PU) algorithm [5] which computed two output digits for every digit product  $x_k^1 x_i^2$ , but had  $f = 2 \min (g, n)$ .

4) Example (r=16, a=9):  $c^1 = c^2 = 0$ ,  $x_k^1 = 9$ ;  $x^2 = 0.\overline{681}$  (internal values shown in decimal).

vari-

ct

$$\frac{\text{PD}(i=0)}{\pi_{k}} = 0 = (16) \ 0 + \overline{0}$$

$$\pi_{k+1} = \overline{54} = (16) \ \overline{3} + \overline{6}$$

$$\pi_{k+2} = \overline{72} = (16) \ \overline{4} + \overline{8}$$

$$K_{k}, K_{k+1} = \overline{3}, \overline{10}$$

$$K_{k}, K_{k+1} = \overline{3}, \overline{10}$$

$$K_{k+1}, K_{k+2} = \overline{10}, \overline{8}$$

$$K_{k+1}, K_{k+2} = \overline{10}, \overline{10}$$

$$K_{k+2}, K_{k+3} = \overline{10}, \overline{10}$$

$$K_{k+3}, K_{k+4} = 0 = (16) \ 0 + \overline{10}, \overline{10}$$

$$K_{k+2}, K_{k+3} = \overline{10}, \overline{10}$$

$$K_{k+3}, K_{k+4} = \overline{10}, \overline{10}, \overline{10}, \overline{10}$$

$$K_{k+3}, K_{k+4} = \overline{10}, \overline{10}, \overline{10}, \overline{10}$$

$$K_{k+3}, K_{k+4} = \overline{10}, \overline{10}$$

# G. The Reconversion Algorithm (RS = 1)

The RS algorithm receives SD digits  $x_i^1$ ,  $x_{i+1}^1$  and reconverts them to conventional (CONV) digits  $y_i$ ,  $y_{i+1}$  such that the CONV radix-r form y represents the same value as the SD radix-r  $\sigma^1 x^1$ . A borrow-propagation must take place because the CONV digits cannot assume negative values.

- 1) Inputs: SD digits  $x_i^1$  on D1,  $x_{i+1}^1$  on D2;  $c^1$  on C1 and C2; input borrow  $b_{i+1}$  on BI (from the positions i+2, i+3 of  $x^1$ ).

- 2) Outputs: CONV digits  $y_i$  on T,  $y_{i+1}$  on S; output borrow  $b_{i-1}$  on B $\emptyset$ ; zero variables  $z_i$ ,  $\sim z_i$ (for  $y_i$ ,  $y_{i+1} = 0$ ) on Z1, Z0.

- 3) Algorithm: For h = i + 1 and h = i compute sequentially

$$b_{h-1} = \begin{cases} 0, & \sigma_h^1 x_h^1 - b_h \ge 0 \\ 1, & \sigma_h^1 x_h^1 - b_h < 0 \end{cases}$$

$$y_h = r b_{h-1} + \sigma_h^1 x_h^1 - b_h.$$

An output borrow  $b_{-n-1}=1$  from the ABE in the most significant position i=-n will occur when the SD number  $\sigma^1 x^1$  is negative. The relationship between the values of  $x^1$  and y is therefore

$$\sigma^{1} x^{1} = y - r^{n+1} b_{-n-1}.$$

The presence of the output borrow indicates that the result y represents the negative value  $\sigma^1 x^1$  as the complement with respect to  $r^{n+1}$  (or "two's complement" when  $r=2^k$  is employed). Connecting the output borrow  $b_{-n-1}$  as the input ("end-around") borrow  $b_q$  into the ABE in the least significant position i=q of  $x^1$  will yield the complement with respect to  $r^{n+1}-1$  (or "one's complement" when  $r=2^k$ ) which is more readily converted to sign-and-magnitude representation of  $\sigma^1 x^1$ . Taking individual digitwise complements  $y_i'=(r-1)-y_i$  will yield the magnitude y' of the negative number  $\sigma^1 x^1$ .

It is to be noted that the RS algorithm yields only two digits of y per ABE, while the previously described reconversion-and-sign unit (RSU) reconverted at least m/2 digits [5]. The number of output wires is the limiting factor in the ABE. An internal arrangement which would utilize some of the ABE input digit lines for CONV digit outputs during the RS algorithm would approximate the RSU capability.

The RS algorithm may be applied as a modifier for the SS and PD algorithms. The BI and B $\phi$  lines must be connected according to the RS specification. The output is the CONV form of the SS sum s or the PD product  $s^k$ .

4) Example

$$(r = 16, a = 9)$$

:  $c^1 = 0$ ;  $x^1 = 0.10\overline{3}5$ .

# H. Conventional-Input Modification (CI = 1)

The similarity between CONV and SD forms is exploited by the CI modification which allows conventional digits  $(0 \le x_i^j \le r - 1)$  as inputs to the ABE and thus provides a convenient conversion from CONV to SD forms. The mixing of SD and CONV-input operands applies to SS, MS, and PD algorithms.

1) CONV-Input Simple Sum (SS=1 and CI=1). The input operand  $x^1$  is a CONV form (sign-and-magnitude). The input  $c^1$ =1 is applied when the sign of  $x^1$  is minus. The digit values  $x_i^1$ ,  $x_{i+1}^1$  are 0 to r-1. The SS algorithm remains unchanged, since the maximum digit sum has the value

$$|K_h|_{\text{max}} = (r-1) + a = r + (a-1)$$

which assures that  $|g_h| \le 1$  and  $|s_i| \le a$  will hold.

2) CONV-Input Product (PD=I and CI=I): The input digit  $x_k^1$  is a CONV form digit ( $0 \le x_k^1 \le r-1$ ). Input C1 receives  $c^1=1$  when the sign of  $x^1$  is minus. The PD algorithm remains unchanged, since the maximum digit product has the value

$$|\pi_{k+h}|_{\max} = a(r-1) = r(a-1) + (r-a)$$

which assures that  $|u_{k+h-1}| \le a-1$  and  $|v_{k+h}| \le a$  will hold.

3) CONV-Input Multiple Sum (MS=1 and CI=1): The digit sum  $\Sigma_i$  of the MS algorithm cannot exceed the limit

$$|\Sigma_i| \le ra + a$$

or  $m \le r + 1$

in order to assume that  $|t_{i-1}| \le a$  and  $|s_i| \le a$  will be satisfied and the result will be SD forms. The maximum number of CONV input digits which satisfies the same requirement is m' such that  $m'(r-1) \le (r+1)a$ , or

$$m' \leq \lfloor a(r+1)/(r-1) \rfloor$$

.

In order to allow the mixing of CONV and SD input operands, we specify the following rule for MS=1 and CI=1:

for every pair of digit lines Dj, D(j+1) with j odd  $(j=1, 3, 5, \cdots)$ , either  $x_i^j$  is a CONV digit and  $x_i^{j+1}=0$ , or  $x_i^j$  and  $x_i^{j+1}$  are both SD digits.

The existence of the CI modification eliminates the need for special conversion algorithms. SD forms with radices  $2^k$  ( $k=2, 3, 4, \cdots$ ) are directly compatible with conventional binary number representations, since binary input operands are accepted by radix  $2^k$  ABE's in the CI mode, and the RS algorithm returns results in binary form.

# I. Significance-Arithmetic Modification (SF = I)

This optional feature is applicable to the SS, MS, PD, and RS algorithms and is compatible with the CI modification. The algorithms are altered to the significant-digit mode [14] by SF = 1. A special "space-zero" digit value  $\phi$  is used to identify nonsignificant positions in SD operands.

In the reconversion (RS) algorithm, input digit values  $x_{i+1}^1 = \phi$  and  $x_i^1 = \phi$  cause the outputs  $y_{i+1} = 0$ ,  $S\phi = 1$  and  $y_i = 0$ ,  $T\phi = 1$ , respectively. The logic 1 outputs on  $S\phi$  and  $T\phi$  explicitly identify the zero value outputs on S and T to be nonsignificant positions in the conventional representation.

Details of the SF-mode algorithms have been described previously [2]-[4], [7]. The general rule requires a "spacezero" output value  $\phi$  whenever at least one input digit in the same position has the value  $\phi$ .

# III. A GRAPH MODEL FOR ARITHMETIC PROCESSOR DESIGN

A single ABE can serve as a digit-serial arithmetic processor. Arrays of ABE's can be arranged for the pipelined hardware implementation of an entire class of functions [6]. The arrangement of ABE's into such arrays can be called arithmetic design, in contrast to the term "logic design," which is needed only within the ABE. Arithmetic design is the process of converting an arithmetic expression to an interconnection diagram of ABE's. The present section presents graph models for algorithms and ABE arrays which make a systematic arithmetic design procedure possible. The procedure has been programmed for computer-aided design of large arithmetic processors.

A combinational arithmetic (CA) net is an acyclically interconnected array of ABE's. Such a net can be described by a directed graph. The graphical representation of CA nets exists in two levels, the algorithm level and the hardware level. At the algorithm level, the CA net is described in terms of a loop-free directed graph with vertices representing fundamental arithmetic, logical, and test operations. At the hardware level the CA net is also described by a loop-free directed graph, but the vertices are specified in terms of the functions performed by the ABE's.

In the description of CA nets, radix-r fixed-point numbers are defined to be of the form

$$x = (x_{-p+1}x_{-p+2}\cdots x_{-1}x_0 \cdot x_1x_2\cdots x_q)$$

and their format is described by the pair of nonnegative integers (p, q), in which p is the length (in digits) of the integer part of x, and q is the length of the fraction part of x.

<sup>&</sup>lt;sup>1</sup> The word "combinational" is used here to denote the absence of feedback loops within the CA net. Arithmetic nets with closed loops are called "iterative."

need adices tional rands

ie RS

T 1970

PD, ificadigit ue  $\phi$  inds. ilues and and be ion.

bed icet in

roed ns be gic

tic

on cys sr-

1

TABLE I

H-Level Vertices

| . 25.150             |                                      |                                           |                                            |                                 |  |  |  |

|----------------------|--------------------------------------|-------------------------------------------|--------------------------------------------|---------------------------------|--|--|--|

| Name and Notation    | Symbol                               | Inputs<br>(Not Modified)                  | Numeric Output Result                      | Multiplicity μ<br>of Output Arc |  |  |  |

| Simple Sum:          | •                                    | 2 SD summands $\pm x^1$ , $\pm x^2$       | single SD word s                           | $\mu = 1$                       |  |  |  |

| SS[p . q; h]         | (+)                                  | n digits each                             | p+q=n+1 digits                             |                                 |  |  |  |

| Multiple Sum:        |                                      | $m$ SD summands $\pm x^1, \dots, \pm x^m$ | double SD word s, t                        | $\mu = 2$                       |  |  |  |

| MS[m; p : q; h]      | #                                    | n digits each                             | p+q=n+1 digits                             | μ-2                             |  |  |  |

| Product:             | SD multiplier $\pm x^1$ , $g$ digits |                                           | $f$ -tuple SD word $s^1, s^2, \cdots, s^g$ | $\mu = f$                       |  |  |  |

| PD[p : q; h]         |                                      | SD multiplicand $\pm x^2$ , n digits      | $x^2$ , <i>n</i> digits $p+q=n+g$ digits   |                                 |  |  |  |

| Reconversion:        | (F)                                  | SD word $\pm x^1$                         | CONV word $y; p+q=n$                       | μ=1                             |  |  |  |

| <b>RS</b> [p . q; h] | (RS)                                 | n digits                                  | output borrow $b_{\text{out}}$             |                                 |  |  |  |

| Storage:             | ©                                    | SD word x <sup>1</sup>                    | the input word                             | $\mu = 1$                       |  |  |  |

| S[p,q;h]             | <b>S</b>                             | n digits                                  |                                            | $\mu-1$                         |  |  |  |

|                      |                                      |                                           |                                            |                                 |  |  |  |

A vertex in either the algorithm or the hardware level aph is identified by the notation

here

OP operation symbol of the vertex

m number of vertices providing inputs

p. q format of the result of the vertex

h number of vertices receiving the output.

he parameter m may be omitted when its value is defined the operation symbol. All input operands are signed-digit umbers except when conventional numbers are explicitly becified. Conventional form results are obtained only from reconversion (RS) vertex.

An arc represents either a numeric result or a logic (two-alued) variable which is generated by its source vertex. The ceiving vertex is identified by the arrowhead of the arc. The transfer of information is unidirectional.

More specific properties of vertices and arcs are presented the following discussion on the two levels of description.

#### The Hardware Level

The hardware-level (*H*-level) graph describes the algorithm which is carried out by the CA net in terms of ABE trays and their interconnections. Five different types of *t*-level vertices are used in an *H*-level graph. They are decribed in detail in Table I. Each *H*-level vertex (*H* vertex) epresents an array of ABE's, except for the storage vertex S hich represents a register.

The operation symbol of an H vertex contains the following information: the ABE algorithm, the additive inverse input specifications, and the algorithm modifiers. The additive inverse is specified for any input operand  $x^j$  by listing its superscript j with an overbar in parentheses following the ABE algorithm symbol. For example  $SS(\overline{1})$  indicates the sim  $(-x^1)+x^2$ ;  $PF(\overline{2})$  indicates the product  $x^1(-x^2)$ ; and

MS( $\overline{1}$ ,  $\overline{4}$ ) [5;  $p \cdot q$ ; h] indicates the sum  $(-x^1)+x^2+x^3+(-x^4)-x^5$ . On the graph, a solid dot at the arrowhead of an arc indicates the additive inverse of the input operand on this arc.

The algorithm modifiers are listed following the ABE algorithm symbol, separated by "slant" symbols. For example,

$$MS(\overline{1}, \overline{4})/CI(5)[5; p.q; h]$$

modifies the previous MS example by specifying that  $x^5$  is a conventional-form operand. The storage vertex S/CI [p,q;h] indicates a CONV form operand, and SS $(\bar{2})$ /SF [p,q;h] indicates a significance-mode addition  $x^1 + (-x^2)$ .

An *H*-level arc (*H* arc) represents an output result (numeric or logic). An identifier tag is attached to an arc. For *numeric* results the tag identifies arithmetic shifts of k positions:  $k \uparrow$  for left, and  $k \downarrow$  for right shift. It also specifies the extraction of certain digits of the result, and identifies the receiving input line. For example, the tag

$$2\uparrow (s_1s_2s_3)|D2$$

identifies that the output digits  $s_1s_2s_3$  are extracted from the sum S and are supplied to the D2 input lines of the receiving H-vertex ABE's with a left shift of two positions. Omission of the digit extraction information means that the entire result is transmitted; zero shifts are also not shown.

An arc which represents a numeric result has an associated *multiplicity*  $\mu$ . The value of  $\mu$  is a function of the source vertex as shown in Table I, in which the outputs are single  $(\mu=1)$ , double  $(\mu=2)$  or f-tuple  $(\mu=f)$  words.

Logic results are obtained from the ABE output lines  $Z1, Z0, T\phi, S\phi, B\phi$ . When an H are represents a single logic variable, the tag contains the variable name, the index of the source ABE, and the receiving input line. For example, Z1(2)|G1 indicates that the Z1 output of the ABE in posi-

TABLE II

A-LEVEL VERTICES

| Operation      | Notation              | Symbol   | Inputs                        | Output                 | H Vertices Needed |

|----------------|-----------------------|----------|-------------------------------|------------------------|-------------------|

| Addition       | $\sum [m;p\cdot q;h]$ | $\Sigma$ | m operands                    | sum                    | SS, MS            |

| Multiplication | $\Pi[p:q;h]$          | (1)      | 2 operands                    | product                | SS, MS, PD        |

| Reconversion   | RS[p . q; h]          | RS       | SD number                     | CONV number            | RS                |

| Storage        | S[p . q; h]           | (S)      | l operand                     | input word             | S                 |

| Logic Op. #    | L#[k; h]              | #)       | k operands                    | 1 logic word           | SS, MS            |

| Test Op. X     | TX[k;h]               | TX       | k operands                    | l logic variable       | SS, MS, RS        |

| Gating         | $G[p \mid q; h]$      | ©        | l operand<br>gate variable G  | input word if G=TRUE   | SS, or S          |

| Merging        | $M[m; p \mid q; h]$   | M        | m operands (only one nonzero) | 1 word (nonzero input) | SS, MS            |

tion i=2 of the source vertex is conveyed to every G1 input of the receiving vertex. A logic variable (TRUE or FALSE) input to a digit line is received as the digit value 1 or 0, respectively.

A fully specified *H*-level graph provides a complete specification for the wiring diagram of the CA net.

#### B. The Algorithm Level

The purpose of the algorithm-level (A-level) graph is to describe the algorithm which is to be computed by the CA net in terms of elementary arithmetic, logic, transfer, test, selection, and storage operations. The H-level description is also acyclic and corresponds to a sequence of typical program (or microprogram) steps, which are identified as vertices on the A-level graph.

The principal constraint which must be satisfied by the A-level graph is that every A vertex should have an equivalent H-level vertex or graph. The conversion from A level to H level is carried out by direct replacement. The resulting H-level graph frequently may be simplified by H-vertex merging, which is discussed in a subsequent section.

The extent of the A-level vertex set is optional with the designer and depends on the complexity of the algorithms which are to be implemented. A typical set of A vertices is listed in Table II. The translations of these vertices to the H level are described in following sections.

The notation for A vertices has the same format as for H vertices, but different operation symbols are used. The additive inverse and algorithm modifier specifications, where applicable, follow the H-level rules.

The A-level vertices of Table II fall into five categories. The arithmetic vertices  $\Sigma$ ,  $\Pi$ , RS (with additive inverse included in each) are used for the implementation of arithmetic. The storage vertex designates storage registers for initial conditions. The logic operation vertex L# is a generic vertex in which # represents any one of the logic operations (NOT, AND, OR, NAND, NOR, EXCLUSIVE OR, EQUIVALENCE, etc.). The test operation vertex TX is also generic. The symbol X represents the test; for example TP, TZ, and TN stand for test-positive, test-zero, and test-negative, respectively. The selection operations are implemented by the use of the gating vertex G and the merging vertex M. These vertices (as well as the logic vertices L#) represent auxiliary uses of the ABE's which may be performed by other types of elements.

A-level arcs have the same meaning as the H-level arcs. The A-level tag specifies a scale factor of  $r^{\pm k}$  instead of an arithmetic shift. Digit extraction remains explicitly specified. The logic (control) signals on the A-level arcs have the values TRUE and FALSE. The multiplicity of the A-level arcs is one, since the representations of the results are not considered at the A level.

# C. Elementary Graphs for Arithmetic Operations

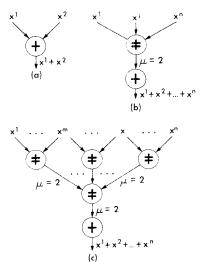

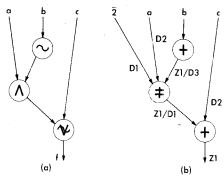

The elementary A-level graphs for addition  $(\Sigma)$  and multiplication  $(\Pi)$  are shown in Fig. 2. The H-level implementation of the A-level addition graph is shown in Fig. 3. Three cases are distinguished:

1) for n=2 operands, an SS vertex replaces the  $\Sigma$  vertex [Fig. 3(a)];

Fig. 2. A-level graphs for (a) addition and (b) multiplication with n operands.

Fig. 3. *H*-level implementation of addition. (a) n = 2. (b)  $2 < n \le m$ . (c)  $m < n \le m \lfloor m/2 \rfloor$ .

- 2) for  $2 < n \le m$  operands, an MS vertex followed by an SS vertex replaces the  $\Sigma$  vertex [Fig. 3(b)];

- 3) for  $m < n \le m \lfloor m/2 \rfloor$  operands, a two-level cascade of MS vertices followed by an SS vertex replaces the  $\Sigma$  vertex [Fig. 3(c)].

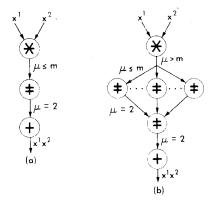

The *H*-level implementation of the *A*-level multiplication graph is shown in Fig. 4. The structure of the *H*-level graph depends on the length (q digits) of the shorter operand  $x^1$ . Two cases are shown in Fig. 4:

- 1) for  $q \le m$ , the  $\Pi$  vertex is replaced by a PD vertex followed by the graph of Fig. 3(b) [Fig. 4(a)];

- 2) for  $m \le q \le m \lfloor m/2 \rfloor$ , the PD vertex must be followed by the graph of Fig. 3(c) [Fig. 4(b)].

Case 1) above should suffice for most multiplications. For example, a radix-16 multiplier  $x^1$  can have up to  $m_{\text{max}} = 17$  digits (or 68 bits) without requiring the graph of Fig. 4(b).

The conversion vertex RS and the storage vertex S remain unchanged in the translation from the A level to the H level. The S vertex is omitted in the graphs of Figs. 3–7, 10, and 12.

Fig. 4. *H*-level implementation of multiplication. (a)  $q \le m$ . (b)  $m < q \le m \lfloor m/2 \rfloor$ .

# D. Graphs for Logic, Test, and Selection Operations

In addition to the arithmetic functions, the A-level graphs may contain vertices which represent logic, test, and selection operations. In this section it is shown how these operations can be implemented at the H level using only the defined algorithms of the ABE.

1) In the Implementation of Logic Operations: The logic values (TRUE, FALSE) are defined in terms of numeric digit values (1, 0):

TRUE

$$\equiv 1$$

, and FALSE  $\equiv 0$ .

The digit values representing k logic variables are designated  $w_1, \dots, w_k$  and are applied to the input digit lines D1, ..., Dk. The output is either z (on line Z1) or  $\sim z$  (on line Z0).

The implementations of the logic operations NOT, AND, OR, NAND, NOR, EQUIVALENCE, and EXCLUSIVE OR by the ABE are as follows (using the SS or MS algorithm):

NOT:

$$\sim w_1 = z(w_1 + 0), \text{ with } k = 1.$$

AND:

$$w_1 \wedge w_2 \wedge \cdots \wedge w_k = z \bigg( \bigg( \sum_{i=1}^k w_i \bigg) - k \bigg),$$

with  $k \leq m-2$  (two inputs accept the constant input value  $k$ ).

OR:

$$w_1 \vee w_2 \vee \cdots \vee w_k = \sim z \left( \sum_{i=1}^k w_i \right),$$

with  $k < m$

NAND:

$$\sim (w_1 \wedge w_2 \wedge \cdots \wedge w_k)$$

$$= \sim z \left( \left( \sum_{i=1}^k w_i \right) - k \right), \text{ with } k \leq m-2.$$

NOR:

$$\sim (w_1 \vee w_2 \vee \cdots \vee w_k) = z \left( \sum_{i=1}^k w_i \right),$$

with  $k \leq m$ .

EQUIVALENCE:

$$\sim (w_1 \neq w_2) = z(w_1 - w_2)$$

, with  $k = 2$ .

EXCLUSIVE OR:  $(w_1 \neq w_2) = z(w_1 + w_2 - 1)$ , with  $k = 2$ .

The notation  $z(f(w_i))$  indicates the z output (on Z1) of an ABE which computes  $f(w_i)$ .

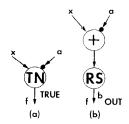

Fig. 5 is lustrates both A-level and H-level graphs for the logic function  $f = \sim [(a \land \sim b) \lor c]$ . The H-level vertices require one ABE per digit of the input word or words; the output is a logic word of the same length.

Fig. 5. Graphs for the logic function  $f = \sim [(a \land \sim b) \lor c]$ . (a) A level. (b) H level.

While it is interesting to note that logic operations can be performed using ABE's, such use is generally not considered practical because of the relatively high complexity and cost of an ABE.

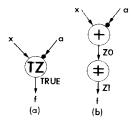

2) Test Operations: Test operations at the H level refer to the test of an arithmetic result: the sum  $\Sigma x^j$  of two or more  $(k \ge 2)$  numbers. The result is a pair of logic variables TRUE and FALSE (FALSE  $\cong \neg$  TRUE), where TRUE = 1 when the test is satisfied, and TRUE = 0 if it is not. Test-positive (TP) is satisfied for  $\Sigma x^j \ge 0$ , test-zero (TZ) for  $\Sigma x^j = 0$ , and test-negative (TN) for  $\Sigma x^j < 0$ .

At the H level the TX vertices are implemented by SS, MS, and RS algorithms. Fig. 6 illustrates the test for x=a which is implemented as TZ for x-a=0 at both levels. At the H level the  $\sim z_i$  outputs for all digits of x-a are summed in an MS vertex, which has z=0 if all  $\sim z_i=0$  at its inputs. Fig. 7 shows the test for x < a, implemented as TN for x-a<0 at both levels. The negative sign of x-a is obtained by the RS vertex which has the borrow  $b_{\text{out}}=1$  from its most significant position when the result is negative. The sign of an SD number is the same as the sign of its most significant nenzero digit; therefore leading zeros may conceal the sign of x-a. This possibility makes a reconversion to CONV form necessary.

More complex tests are implemented as combinations of the elementary tests. For example, the test for  $a \le x \le b$  is implemented as the logic AND of two TN tests:

$$f = [(a - x) < 0] \land [(x - b) < 0]$$

A more detailed discussion of testing is presented in [7].

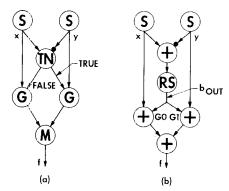

3) Selection Operations: The gating (G) and merging (M) H-level vertices provide the equivalents of selective gating (AND-OR) operations in conventional logic circuitry. They are included to demonstrate the extent of the functions provided by CA nets. Their use is not practical when simpler logic circuits are available for this purpose.

An illustration of the use of G and M vertices is shown in Fig. 8. The function of the CA net is as follows:

$$f = \begin{cases} x, & x \ge y \\ y, & x < y. \end{cases}$$

The gating function (replacing AND) is implemented by SS vertices (S can also be used). The merging function (replacing

Fig. 6. Graphs for the zero test x-a=0. (a) A level. (b) H level.

Fig. 7. Graphs for the negative test x - a < 0. (a) A level. (b) H level.

Fig. 8. Graphs for the selection: f = x if  $x \ge y$ ; f = y if x < y. (a) A level, (b) H level.

OR) uses an SS vertex; an MS vertex is needed for more than two inputs.

#### E. Iterative Arithmetic Nets

The acyclic nature of the CA net may require too many ABE's to implement the net at an acceptable cost. In this case a smaller CA net can be designed and used iteratively to compute the same function. Such an iterative arithmetic (IA) net requires fewer ABE's and more time than the CA net which computes the same function in one pass through the net.

The CA net provides a reference point for the design of a processor. It requires the greatest number of ABE's and has the lowest computing time. An entire set of IA net designs usually can be derived from the CA net; these IA nets have gradually decreasing cost and increasing time requirements. The IA net with the highest acceptable computing time will yield the least costly design. The graph models of the original CA net explicitly display the regularities of the CA net structure and therefore facilitate the IA net design.

Illustrations of IA nets are provided by two nets for the implementation of division [4], [16]. A further example of an IA net is found in the design of an ABE-array arithmetic processor which computes a large class of functions [6]. The same processor also employs pipelining of CA nets in

der to achieve the highest possible rate of utilization. The orage registers at the output of the ABE are provided in der to make pipelining of CA nets feasible.

#### IV. CA NETS FOR THE EVALUATION OF POLYNOMIALS

#### . The Algorithm and Its Graphs

1.

el.

an

ny

uis

ly

ic

A

ţh

a d In this section we consider the application of CA nets to olynomial evaluation. A common method of approximating a given function is to employ polynomial approximation [8], [9]. The application of CA nets to polynomial valuation will serve as an illustration of their potential pplication. A method proposed by Estrin [10] permits the astest evaluation of explicit polynomials when sufficient parallel computing capacity is provided. The method to compute the *n*th-degree polynomial

$$p(x) = a_0 + a_1 x + \dots + a_n x^n$$

requires the computation of the terms  $C_i^{(1)}$

$$C_i^{(1)} = a_i + x a_{i+1}, \quad i = 0, 2, \dots, 2 | n/2 |$$

**followed** by successive computations of terms  $C_i^{(j)}$  for  $j=2,\dots,m$ :

$$C_{i}^{(2)} = C_{i}^{(1)} + x^{2}C_{i+2}^{(1)}, \quad i = 0, 4, \cdots, 4\lfloor n/4 \rfloor$$

$$\vdots$$

$$C_{i}^{(m)} = C_{i}^{(m-1)} + x^{2^{m-1}}C_{i+2^{m-1}}^{(m-1)}, \quad i = 0, 2^{m}, \cdots, 2^{m}\lfloor n/2^{m}\rfloor.$$

This process will terminate when

$$m = \lfloor \log_2 n \rfloor + 1$$

$$p(x) = C_0^{(m)}.$$

The procedure corresponds to the factoring:

$$p(x) = a_0 + a_1 x + x^2 (a_2 + a_3 x)$$

$$+ x^4 [a_4 + a_5 x + x^2 (a_6 + a_7 x)]$$

$$+ x^8 [a_8 + a_9 x + x^2 (a_{10} + a_{11} x)]$$

$$+ x^4 (a_{12} + a_{13} x + x^2 (a_{14} + a_{15} x))] + \cdots$$

We notice that for each j, all  $C_i^{(j)}$  may be computed simultaneously in one multiplication time plus one addition time. Therefore, the minimum time to compute p(x) using this algorithm is

$$\tau = \lceil \log_2 n \rceil + 1$$

multiplication–addition times.

It is necessary to have a sufficient number of arithmetic units to compute  $C_i^{(j)}$  simultaneously for any j in order to achieve this minimum time. This requirement can be met by a CA net in which each vertex performs addition and multiplication.

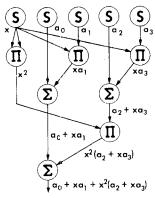

A simple example illustrating how CA nets are organized to evaluate third-degree polynomials using Estrin's method is shown in Fig. 9. Here the evaluation of a third-degree polynomial at the A level takes  $\lfloor \log_2 3 \rfloor + 1 = 2$  units of time required by a pair of  $\Pi - \Sigma$  vertices. The speed at the H level requires further information. The delay through one vertex in the H-level CA net is the delay through one ABE. The total delay through the H-level CA net is equal to the num-

Fig. 9. A-level graph for the evaluation of polynomials (degree 3).

ber of vertices along the longest information flow path of the net. The configuration and complexity of the *H*-level CA net depend not only on the topology of the *A*-level CA net, but also on the precision of the data word.

The cost of the CA net is defined as the count of ABE's in the net. It is a function of the degree of the polynomial and of the precision of the data word. Error in a CA net comes only from round-off operations if all input data are assumed to be free from inherent errors. Precision controls the size of the round-off errors. Since precision thus affects the speed, cost, and error of the CA net, it will be used, together with the degree *n* of the polynomial, as the independent variable in the study of speed, cost, and error of the CA net.

### B. Complexity and Speed of the CA Net

In an A-level CA net for evaluating the polynomial

$$p(x) = \sum_{i=0}^{n} a_i x^i$$

the number of storage (S) vertices N(S) is

$$N(S) = n + 2$$

because there are n+1 coefficients  $a_i$ ,  $i=0, 1, 2, \dots, n$ , and the independent variable x.

The number of multiplication vertices in the net is

$$N(\Pi) = n + \lfloor \log_2 n \rfloor$$

and the number of addition vertices is

$$N(\Sigma) = n$$

.

The speed of this A-level CA net is

$$\tau = \lceil \log_2 n \rceil + 1 \ \Pi \Sigma \text{ time units}$$

where one  $\Pi\Sigma$  time unit is the delay through one  $\Pi$ - $\Sigma$  pair of vertices.

The H-level implementation of the A-level vertex  $\Pi$  is shown in Fig. 4. One PD vertex and one SS vertex are needed, i.e.,

$$N(PD) = N(SS) = N(\Pi).$$

The count of the MS vertices depends on the precision of the operands. Given the precision  $q = \min(g, n+1)$  according to Table I, there are two cases:

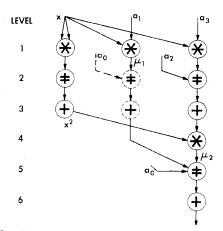

Fig. 10. H-level translation of the A-level graph of Fig. 9.

- 1) a single MS vertex is sufficient when  $q \le m$ ;

- 2) a two-level cascade of MS vertices is required for  $m < q \le m |m/2|$ .

The one-level cascade is sufficient for most cases. For instance, in the radix 16 and m=17 example a precision of 17 radix-16 digits can be accommodated. The number of MS vertices in the first level of the cascade of case 2) varies from 1 to  $\lfloor m/2 \rfloor$  as q increases, and is given by

$$K = [(q-m)/(m-2)].$$

The second level always contains one MS vertex.

It must be noted that in the formation of the term  $a_i + a_{i+1}x$ , the summation in the MS vertex includes the single word  $a_i$  along with the result word of the PD vertex. In this case the preceding results apply when q is taken to be the sum of the multiplicities of the product  $a_{i+1}x$  and the word  $a_i$ . A direct translation of the A-level net to the H level is shown in Fig. 10 (including the dotted-line vertices) for  $q \le m$ .

The detailed count of ABE's in the SS, MS, and PD vertices has been discussed in the algorithm description of Section II.

# C. Computer-Aided CA Net Design

The graph of a CA net displays its structure and is a convenient means to design a CA net for relatively simple problems. For more complex problems, however, the graphical approach becomes tedious, especially when many designs are needed for purposes of evaluation. A programming effort was undertaken to demonstrate that a graphical CA net may be represented by tables acceptable to conventional computers, and that nontrivial operations on these tables can be performed by the program. The program is so far limited to evaluating polynomials up to 15th degree with Estrin's method. It is written in FORTRAN IV for running on the SDS Sigma 7 computer of the Digital Technology Research group at UCLA.

The topological relations among the vertices and arcs of a graph can be described by a family of matrices (connection matrices, precedence matrices, etc.) or threaded lists. The list representation was adopted for the following reasons. The description of vertices and arcs in a CA net consists of

many parameters, and it is expected that, as problems ge more complicated, more attributes will need to be added Consequently, greater numbers of matrices are required to fully describe a CA net; this may result in an overflow of memory capacity. On the other hand, a threaded list is much less storage consuming, even though searching through the threaded list may be slower.

The program consists of four parts:

1) generation of CA-15 net for evaluating

$$p(x) = \sum_{j=0}^{1.5} a_j x^j$$

at the A level,

2) generation of CA-i net for evaluating

$$p(x) = \sum_{j=0}^{i} a_j x^j \text{ with } i \le 15$$

at the A level from the CA-15 net;

- 3) translation of CA-i net from A level to H level;

- 4) simplification of the *H*-level CA-*i* net.

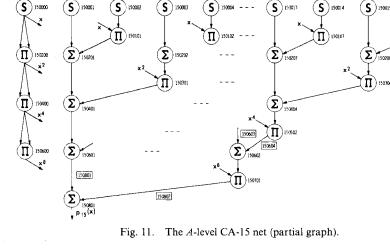

The first step is to generate tables fully describing the topological configuration of a CA net for evaluating a 15th degree polynomial at the A level. The graph shown in Fig. 11 is translated to a tabular form. With these tables as a base, the tables describing CA nets at the A level for polynomials up to degree 15 are obtained through a process of elimination. A direct-replacement translation from the A level to the H level then takes place to provide more information about cost, speed, and accuracy. (Figs. 3 and 4 show parts of the translation process.) Redundancy may exist in the H-level tables thus obtained, because the translation is not simplified. A final simplification step eliminates redundancies in the H-level CA net.

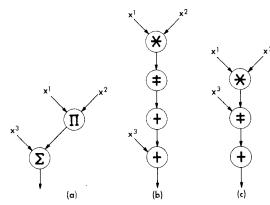

An example of simplification is given in Fig. 12. A typical portion of the CA net of Fig. 11 is shown in Fig. 12(a). A direct translation would result in an H-level CA net shown in Fig. 12(b). If the output multiplicity of the PD(\*) vertex does not exceed m-1, the input capacity of the MS( $\pm$ ) vertex is not filled. Consequently, the second SS(+) vertex can be removed by connecting its input to the multiple-sum vertex. Fig. 12(c) is the simplified form of the H-level net

Another example of simplification is shown in Fig. 10 Translation to the H level by direct replacement will yield the graph including the dashed-line vertices at levels 2 and 3 The SS vertex at level 3 is removed if one unused input exists in the level-5 MS vertex. Furthermore, the dashed line MS vertex at level 2 is removed if  $\mu_1 + \mu_2 + 1 \le m$  holds at the level-5 MS vertex.

A detailed description of the implementation of the CA-net design program is presented in [7]. The existence of the CA-net design program allows the designer to try several designs with differing choices of precision and with differing values of the polynomial order. The program tabulates the cost (in ABE's) and the speed [in ABE delays] for every design. The study of tradeoffs between speed, cost, precision and error of approximation becomes feasible even for large CA nets and for numerous changes in these parameters.

as get dded. ed to ow of much h the

Fig. 12. Simplification by vertex merging at the H level. (a) A level. (b) H level, direct. (c) H level, simplified.

#### V. CURRENT WORK

The study of arithmetic building blocks has been stimuted by the Variable Structure Computer research at the omputer Science Department of UCLA and is being conacted as part of this research project [10], [11]. The ABE intended to serve as a standard inventory item of the ariable structure resources.

Work is currently progressing in three directions: the esign of a pipelined function generator to replace arithmetical subroutines [6], the study of the computational omplexity aspects of signed-digit arithmetic [15], and the ogic design of a radix-16 ABE for LSI implementation.

The present paper omits the logic design aspects of the BE in order to avoid excessive length. The design follows he approach of [4] and [7] and will be reported in a septrate presentation.

# REFERENCES

- [1] A. Avižienis, "Signed-digit number representations for fast parallel arithmetic," IRE Trans. Electronic Computers, vol. EC-10, pp. 389-400. September 1961.

- "On a flexible implementation of digital computer arithmetic," Information Processing 1962, C. M. Popplewell, Ed. Amsterdam: North-Holland, 1963, pp. 664-670.

- -, "Binary-compatible signed-digit arithmetic," 1964 Fall Joint Computer Conf., AFIPS Proc., vol. 26, pt. 1, Baltimore, Md.: Spartan, 1964, pp. 663-672.

- -, "Arithmetic microsystems for the synthesis of function genera-

- tors," *Proc. IEEE*, vol. 54, pp. 1910–1919, December 1966. [5] A. Avižienis and C. Tung, "Design of combinational arithmetic nets," Dig. 1st Ann. IEEE Computer Conf. (Chicago, Ill.), pp. 25-28, September 6-8, 1967.

- [6] C. Tung and A. Avižienis, "Combinational arithmetic systems for the approximation of functions." 1970 Spring Joint Computer Conf., AFIPS Proc., vol. 36. Washington, D. C.: Spartan, 1970, pp. 95-107.

- [7] C. Tung, "A combinational arithmetic function generation system," Ph.D. dissertation, University of California, Los Angeles, Engrg. Rept. 68-29, June 1968

- [8] C. W. Clenshaw, Chebyshev Series for Mathematical Functions, Mathematical Tables, vol. 5. London: National Physical Lab.,

- W. Dorn, "Generalization of Horner's rule for polynomial evaluation," IBM J. Res. Develop., vol. 6, pp. 239-245, April 1962.

- [10] G. Estrin, "Organization of computer systems—the fixed plus variable structure computer," 1960 Western Joint Computer Conf., vol. 17, pp. 33-40.

- [11] G. Estrin, B. Bussell, R. Turn, and J. Bibb, "Parallel processing in a restructurable computer system," IRE Trans. Electronic Computers, vol. EC-12, pp. 747-755, December 1963.

- [12] M. J. Flynn, "Very high-speed computing systems," Proc. IEEE, vol. 54, pp. 1901-1909, December 1966.

- [13] R. A. Henle and L. O. Hill, "Integrated computer circuits—past, present, and future," Proc. IEEE, vol. 54, pp. 1849-1860, December

- [14] N. Metropolis and R. L. Ashenhurst, "Significant digit computer arithmetic," IRE Trans. Electronic Computers, vol. EC-7, pp. 265-267, December 1958.

- [15] A. Avižienis, "On the problem of computational time and complexity of arithmetic functions," Proc. ACM Symp. on the Theory of Computing (Los Angeles, Calif.), pp. 255-258, May 5-6, 1969.

- C. Tung, "Signed-digit division using combinational arithmetic nets," IEEE Trans. Computers, this issue, pp. 746-748.

the 15th 1 in s as for cess

the ind 4 nay slaites

cal wn tex +) tex ımı

et. 10. eld 13. ut :d-

he

ds