## A COMPARISON OF TWO APPROACHES TO MULTI-OPERAND BINARY ADDITION

D.E. Atkins and S.C. Ong

Program in Computer, Information and Control Engineering and

Systems Engineering Laboratory

Department of Electrical and Computer Engineering

The University of Michigan

Ann Arbor 48109

#### INTRODUCTION

This paper presents the results of one phase of a study concerning methods for addition of P>2 numbers, each encoded as a vector of digits (digit vector) of length N. Such multi-operand addition has been studied most often in the context of reducing a set of partial products to a single result in the implementation of multiplication. More generalized multi-operand addition, most notably in the form of inner product calculations is, however, central to numerous scientific applications of digital computers. Although multioperand addition is trivially accomplished by accumulation (iteration in time) in any general purpose machine, demands for very high-speed computation, typified by 2- and 3-D signal processing prompt implementation of dedicated, hardware-intensive structures for multi-operand addition. This study, for example, is motivated in part by requirements for rapid simultaneous addition of up to 100, 16-bit operands in the design of a dedicated processor for real-time reconstruction of 3-D images of the beating heart and breathing lungs [1].

The variety of tradeoffs between iteration in time and hardware, the application of the commutative and transitive properties of addition, and the possibility of using redundant encoding of numbers which restrict carry propagation give rise to numerous published schemes for multi-operand addition. Examples of time-intensive sequential schemes are discussed in [2-8], and arrays of carry-save adders (deferred carry assimililation structures) are cited in [9-15]. If we consider the rows of digit vectors to be reduced by addition to be a matrix of digits, the columns of the matrix may be simultaneously compressed from P digits to a vector of about length log P digits. Subsequent column compressions will lead to a single digit vector representation of the sum of the P operands. These "column compression" ideas are included in [3,10,11,16,17,18]. References [19-21] describe schemes which fall in the middle ground with respect to a time-hardware tradeoff.

Our broad goal is to revisit (especially the elegant work of Dadda [10]) and perhaps extend this

literature in light of advances in LSI technology, demands for increased arithmetic computation speed, and innovations in parallel computer architecture. We also intend to study the time-hardware complexity of multi-operand addition across a broad set of finite number representation systems [22], including as a special case, variations in radix. In this paper, however, we restrict ourselves to the specific topic of a cost and performance comparison of multi-operand adders for unsigned, binary encoded operands implemented in the following two ways suggested by commercially available MSI components:

- As a tree of (nonredundant, carrypropagate) adders which accept two digitvectors and produce a one digit-vector result;

- (2) As a tree of "carry-save" adders which accept three digit vectors and produce a two digit-vector result.

The analysis will be conducted assuming three variables, namely: number of operands P, length of the operands N (all uniform length), and the maximum fan-in of the device gates, FANIN.

Informally the problem is as follows: carry-save adders produce a result rapidly since they avoid "solving" the carry-propagation recurrence at the expense of reduced operand compression (3-to-2 instead of 2-to-1). Adders which assimilate all carries yield a 2-to-1 operand compression but require auxiliary logic (carry-lookahead logic) in order to "solve" the carry recurrence. Which is "better" for multi-operand addition? Carry-ripple adders avoid the "lookahead" logic but, in general, would be so much slower than a carry-save adder that a comparison would be uninteresting.

In the next section we derive cost and performance measures for a tree of 2-to-1, carry-lookahead structures. In subsequent sections, we perform the analogous task for a tree of 3-to-2 carry-save structures, compare the results, and then recompare with the introduction of restrictions on packaging and chip pin-outs. Since for most of the cost and performance functions we

This work was supported by the National Science Foundation, Division of Mathematical and Computer Science under Grant No. MCS-77-03310 and by the U.S. Public Health Service Grants HL-04664, RR-00007 from the National Institutes of Health.

have not found a closed form expression, APL versions of the cost and performance functions are used. A review of the principles of binary carrylookahead and carry-save addders may be found in [23,24].

COST AND PERFORMANCE OF TWO-TO-ONE STRUCTURES

In this section we first develop a cost and performance function for carry-lookahead adder which accepts two N-bit operands and produces a N+1-bit result. We then apply these results to the analysis of a tree structure which accepts P, N-bit operands to produce one N+log P-bit result.

#### Two operand carry-lookahead adder

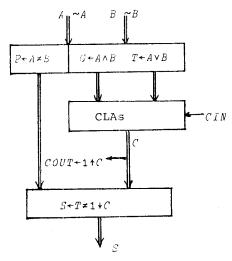

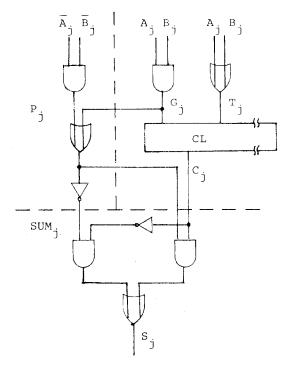

Consider the block diagram in Figure 1 which combines two N-bit operands, A and B, to form a sum S using so-called carry-lookahead techniques to compute the carry vector in the CL box. Assuming that the delay through a logic gate is a uniform time t, then it requires time t to produce carry transmission (T) and generate terms (G). Assuming that an inverter also requires time t, it furthermore requires at best 2t to produce carries C in the CL and 3t more to develop S. For each operand bit, it requires one gate for T, one for G, 3 for P and 4 for S as shown in Figure 2.

Figure 1. Block diagram of a carry-lookahead adder.

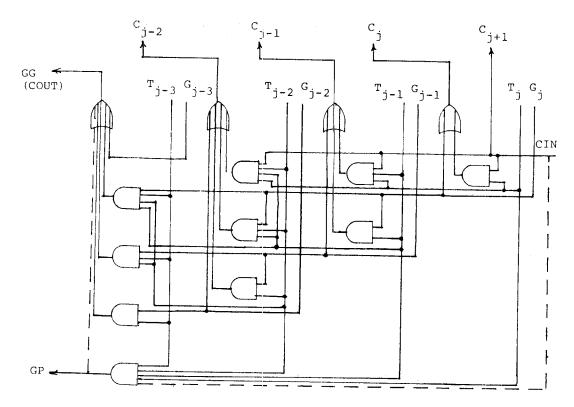

The structure of a CL network which produces 4 carry bits plus a group generate and a group propagate is shown in Figure 3. The dotted lines show a slight variation which is used to produce a true group carry-out at certain boundary positions of both the balanced and optimized adder trees to be presented shortly. The number of positions across which lookahead takes place (i.e. the length of the carry vector produced) is restricted by the fan-in of the constituent gates assuming that operation time does not exceed 2t. If we further impose the restriction that the true group carry must be formed without introducing more delay, then the number of bit positions across which first-level lookahead takes place (NUMBIT) is given by

Figure 2. One position of the carry-lookahead adder.

$$NUMBIT = FANIN-1 \tag{1}$$

where FANIN is the maximum number of inputs to a primitive gate. In the following equations, for convenience, we use "NUMBIT" as an implicit function of "FANIN".

The number of gates required to implement a CL structure of the type shown in Figure 3 across NUMBIT bits, is the sum of NUMBIT OR gates and a geometric series of AND gates, namely

$$G1'(FANIN) = .5x(NUMBIT^2 + 3xNUMBIT),$$

(2)

where NUMBIT is defined in terms of FANIN in Equation (1).

In general, the operand length, N, is greater than NUMBIT and consequently, multi-level carry-lookahead across groups of first level units may be employed. The number of levels of NUMBIT-wide CL units required to produce the carry vector of length N is given by

$$L1(FANIN,N) = \lceil \log_{NUMBTT} N \rceil$$

(3)

where  $\lceil x \rceil$  is the ceiling function, i.e. the smallest integer  $\geq x$ .

$$T1(L1(FANIN,N)) = 2 \times (2 \times L1(FANIN,N)+1) \times t.$$

(4)

Figure 3. Carry lookahead (CL) unit with NUMBIT=4.

The  $\,$  number of CL units is given by L1 terms of the following

U1(N, FANIN) = [N/NUMBIT]+[([N/NUMBIT])/NUMBIT]+...

(5)

where  $\lfloor x \rfloor$  is the floor function, i.e. greatest integer  $\leq x$ .

The number of gates required to implement the two N-bit operand carry-lookahead adder is

$G1(N, FANIN) = 9 \times N + U1(N, FANIN) \times G1'(FANIN)$  (6)

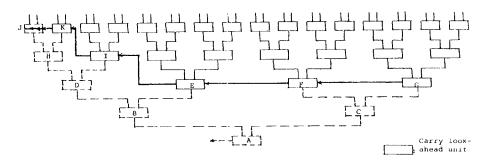

As an example, the structure consisting of both the solid and dashed nodes shown in Figure 4 is the tree for the case N=32, FANIN=3. In this case, 31 CL units of width 2 are required and the structure produces the final sum in time 22t. The balanced tree of CL units does not, in general, yield the smallest propagation delay. At some point toward the root of the tree it becomes faster to propagate the carries laterally rather than forward and back down from a higher level CL.

Figure 4, minus the dashed boxes together with the lateral carry inter-connections, yields higher performance with less hardware than the full balanced tree. The pruning of the tree is reasoned as follows:

- (1) It takes 4t more delay and 1 more CL unit to add a level to the tree, but only 2t more, without increasing the number of CL units, to form the group carry-out. (See Figure 3). Thus the propagation route from module C to B in Figure 4 saves 2t in time and 1 CL in hardware compared to the C to A to B route.

- (2) The routes G-F-E-D and G-C-B-D both require delay 6t. However, the former saves two CL units.

- (3) It takes the same delay, 4t, for both E-I-H and E-D-H but the former saves 1 CL unit. Similarly, H can be deleted by connecting the carry-out term from I to the carry-in of K.

- (4) We need 5t in K to form the sum of the most significant bit, either 2t in the CL plus 3t to form S(sum), or 2t for carry-ripple and 3t for S. In other words, in some parts of the structure, carry-lookahead had no speed advantage over carry ripple.

Following these principles, the minimal gate delay and number of CL units required were computed constructively in the form of APL functions, DELAYNUM and UNIT. These are listed in Figure 5.

Figure 4. Tree of CL units to produce (N+1)-bit carry vector.

```

\nabla Z+DELAYNUM N; K

A THE NUMBER OF GATE DELAY FOR CARRY LOOK-AHEAD ADDER

[1]

A NUMBIT IS DEFINED EXTERNALLY

[2]

[3]

Z + 0

[4]

\rightarrow (0 \ge N)/0

[5]

Z \leftarrow 4

[6]

\rightarrow (1 \geq N)/0

[7]

2+6

\rightarrow (N \leq NUMBIT+1)/0

[8]

K \leftarrow \lceil NUMBIT \otimes 1 + N \times NUMBIT - 1

[9]

[10]

Z \leftarrow 4 \times K - 1

\rightarrow (N \leq (((NUMBIT \starK -1) -1) \div NUMBIT -1) + NUMBIT \starK -2)/0

[11]

[12]

Z+Z+2

\nabla Z \leftarrow UNIT N; TN; I; J; K; L

[1]

A THE NUMBER OF CLA UNITS

A NUMBIT IS DEFINED EXTERNALLY

[2]

A THE FUNCTION WHICH IS DERIVED CONSTRUCTIVELY IS EFFECTIVE

[3]

IF (1) WORDS LENGTH IS LESS THAN 150

[4]

8

(2) 3 \le FANIN \le 9

[5]

[6]

Z \leftarrow 0

[33]

Z+30

\rightarrow (0 < TN + N - 67) / A1

\rightarrow (N \leq 2)/0

[34]

[7]

[35]

[8]

\rightarrow (NUMBIT>2)/THREE

Z←17

\rightarrow (0 < TN \leftarrow N \sim 40) / A1

[9]

[36]

Z \leftarrow 1

[10]

\rightarrow (N \leq 4)/0

[37]

I+2

[38]

[11]

Z + 8

Z+2

[12]

\rightarrow ( \tilde{N} \leq 5 ) / 0

[39]

\rightarrow (0 < TN \leftarrow N - 22) / A1

Z \leftarrow 4

[13]

[40]

I \leftarrow 1

[14]

J \leftarrow 4

[41]

\rightarrow (0 < TN \leftarrow N - 13) / A1

[15]

TN \leftarrow N - 5

[42]

K+2

[16]

Z+N-J

[43]

Z+1

[17]

\rightarrow (0 \geq TN \leftarrow TN - 2 \star I)/0

[44]

\rightarrow (0 < TN \leftarrow N - 7) / A1

[18]

Z+Z-1

[45]

T'N \leftarrow N - 4

[46]

[19]

\rightarrow (0 \ge TN + TN - 2 \times I) / 0

Z \leftarrow 0

[20]

Z+Z+1

[47]

A1:Z+Z+1

[48]

\rightarrow (0 \ge TN \leftarrow TN - 1)/0

[21]

\rightarrow (0 \ge TN \leftarrow TN - 2 \star I)/0

[22]

I \leftarrow I + 1

[49]

Z+Z+1

\rightarrow ( 0 \ge T'N \leftarrow TN - 2 ) / 0

[23]

J+J+1

[50]

[24]

[51]

→16

\rightarrow (1 \leq K + K - 1) / A1

[25] THREE: → (NUMBIT>3)/MORE

[52]

Z+Z+1

[26]

Z \leftarrow 1

[53]

\rightarrow (0 \geq T'N \leftarrow T'N - 1)/0

[27]

\rightarrow (N \leq 4)/0

[54]

Z \leftarrow Z + 1

[28]

+(N>158)/81

[55]

\rightarrow (0 \geq TN \leftarrow TN - 3)/0

[29]

I \leftarrow K \leftarrow 1

[56]

Z \leftarrow Z + 1

[30]

J+2

[57]

\rightarrow (0 \geq T'N \leftarrow T'N - 2)/0

[58]

Z←57

+ (1≤I+I-1)/A1

[31]

\rightarrow (0 < TN + N - 121) / A1

[59]

[32]

Z \leftarrow Z + 1

```

Figure 5. Listing of APL functions DELAYNUM and UNIT.

```

[60] +(0 \ge TN + TN - 1)/0

[95] TN+TN+NUMBIT

[61] Z+Z+1

[96] A2:Z+Z+1

[62] \rightarrow (0 \ge TN + TN - 2)/0

[97] \rightarrow (0 \ge TN + TN - 1)/0

[63] Z+Z+1

[98] Z \leftarrow Z + 1

[64]

\rightarrow (0 \ge TN + TN - 2)/0

[99]

\rightarrow (0\geqTN\leftarrowTN+1-NUMBIT)/0

[65]

2+2+1

[100] Z+Z+1

[66]

\rightarrow (0 \geq TN+TN-3)/0

[101] \rightarrow (0\geqTN\leftarrowTN-1)/0

[67] Z+Z+1

[102] Z+Z+1

[68]

\rightarrow (0 \ge TN + TN - 2)/0

[103] \rightarrow (0\geqTN\leftarrowTN-NUMBIT)/0

[69]

Z+Z+1

[104] \rightarrow (0 < I + I - 1)/102

[70]

\rightarrow (0 \ge TN + TN - 2)/0

[105] Z+Z+1

[71]

Z+Z+1

[106] \rightarrow (0\geqTN+TN+1-NUMBIT)/0

[72]

\rightarrow (0 \geq TN \leftarrow TN - 1)/0

[107] Z+Z+1

[73]

Z+Z+1

[108] \rightarrow (0 \geq TN+TN-1)/0

[74] \rightarrow (0 \ge TN + TN - 3)/0

[109] Z+Z+1

[75] Z+Z+1

[110] \rightarrow (0 \ge TN + TN + 1 - NUMBIT)/0

[76] \rightarrow (0 \ge TN + TN - 2)/0

[111] Z \leftarrow Z + 1

[77]

\rightarrow (1 \leq J + J - 1) / A1

[112] \rightarrow (0 \ge TN + TN - 2)/0

[78] MORE:Z+1

[113] I \leftarrow NUMBIT - 2

\rightarrow (0 \geq N - NUMBIT+1)/0

[797

[114] Z+Z+1

[80]

\rightarrow (0 \geq TN+N-1+NUMBIT×1+NUMBIT×1+2×NUMBIT)/83[115] \rightarrow (0 \geq TN+TN-NUMBIT)/0

[81]

'OUT OF RANGE'

[116] \rightarrow (0 < I + I - 1)/114

[82] →0

[117] Z+Z+1

[83] I \leftarrow J \leftarrow NUMBIT - 2

[118] \rightarrow (0 \geq TN\leftarrow TN+1\rightarrow NUMBIT)/0

[84] \quad Z \leftarrow 1 + (NUMBIT + 1) + 2

[119] \rightarrow (0<J+J-1)/109

[857

\rightarrow (0 < TN \leftarrow TN + NUMBIT \star 3) / A2

[120] Z+Z+1

[86]

Z+2 \times NUMBIT+1

[121] \rightarrow (0 \ge TN \leftarrow TN + 1 - NUMBIT)/0

[87]

[122] Z+Z+1

[88]

+(0 < TN+N-1+NUMBIT \times 1+NUMBIT \times 2)/A2

[123] \rightarrow (0 \ge TN \leftarrow TN - 1)/0

[89]

Z \leftarrow NUMBIT + 1

[124] I+NUMBIT-2

[90]

\rightarrow (0 < TN + TN + NUMBIT * 2) / A2

[125] Z+Z+1

[91] Z+1

[126] \rightarrow (0\geqTN+TN-NUMBIT)/0

[127] \rightarrow (0<I+I-1)/125

[92] I+I-1

[128] Z+Z+1

```

Figure 5 (cont.). Listing of APL functions DELAYNUM and UNIT.

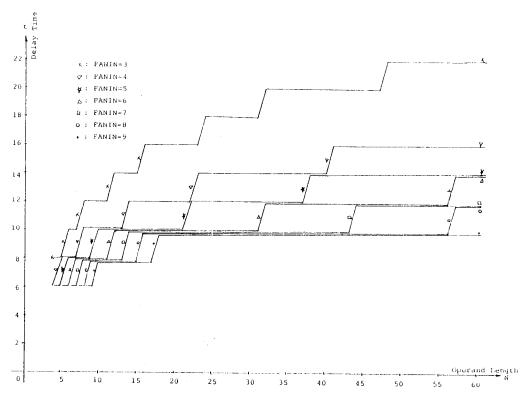

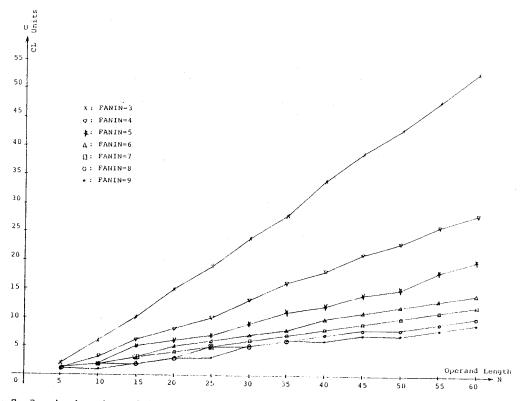

Figures 6 and 7 are graphs of the results for N $\leq$ 60 and 3 $\leq$  FANIN  $\leq$ 9. These results are up to 20% less than values predicted by Equations (4) and (5) which assume a balanced full tree, and are up to 50% less than the upper bounds on component count and speed for carry-lookahead adders given by Kuck in [8].

## Multi-operand carry-lookahead adder

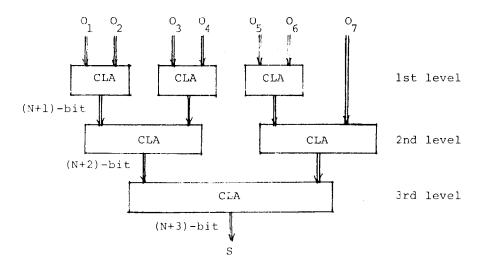

We are now in the position to analyze a multi-operand structure realized as a tree of two-operand adders each of which employes multi-level carry-lookahead techniques as shown in Figure 8. Note that the operand lengths are N+i-1 at the ith level. The number of levels of 2-to-1 adders to combined  $P\geq 2$  operands is given by

$$L2(P) = \lceil \log_2 P \rceil, \tag{7}$$

where  $\lceil x \rceil$  is the ceiling function, i.e. the smallest integer greater than or equal to x.

Now let I21(P,i) and J21(P,i) be the number of input operands and the number of carry-lookahead adders (CLA's), respectively, at the ith level. I21(P,i) equals the number of operand outputs from level i-1 plus the number of operands which have not been combined at a previous level. It follows

that

$$I21(P,i) = J21(P,i-1)+I21(P,i-1)-2xJ21(P,i-1)$$

(8)

with I21(P, 1) = P.

$$J21(P,i)=[I21(P,i)/2]$$

(9)

The total number of CLA units is [25]

$$U2'(P) = P-1.$$

(10)

Upper bounds on performance and number of gates may be derived from Equations (1-9). In particular, the total time to compute the P, N-bit operand sum is the total of the delay at each level, namely

$$T2(N,FANIN,P) = \sum_{i=1}^{L2(P)} T1(L1(FANIN,N+i-1)).$$

(11)

A bound on the number of CL units required is the sum of the number of CLA groups times the number of CL units per CLA for each level.

Figure 6. Operational delay vs. operand length and fan-in for carry-lookahead adder.

Figure 7. Required number of CL units vs. operand length and fanin for carry-lookahead adder.

Figure 8. Example of 2-to-1 tree for P=7.

$$U2(N,FANIN,P) = \sum_{i=1}^{L2(P)} J21(P,i) \times U1(N+i-1,FANIN). (12)$$

The total number of gates required for the entire structure is bounded by

G2(N,FANIN,P) =

$$\sum_{i=1}^{L2(P)} J21(P,i) \times G1(N+i-1,FANIN). (13)$$

Our numerical results are based, not upon these bounds, but rather upon the optimized CLÁ structures described previously. The functions analogous to T2, U2 and G2 for these optimized structures are denoted T2", U2", and G2", respectively. These functions are evaluated using the APL functions CIME21, CLA21, and GATE21 as listed in Figure 9.

COST AND PERFORMANCE OF THREE-TO-TWO STRUCTURES

## Three operand carry-save adder

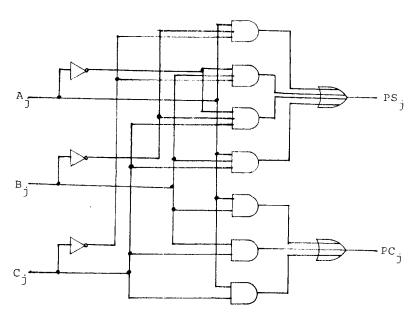

By "carry-save adder" (CSA) we refer to a logic network which accepts three digit vector operands and produces two, the sum of which is equal to the sum of the three. The truth table for the specific version assumed here is shown in Table 1. This structure is a special case of the carry-save/ borrow-save networks studied by Robertson in [26]. Figure 10 shows a gate-level realization of one position of a CSA for FANIN=4. If FANIN=3 then four levels are required, i.e.

$$T3(FANIN) = 3t \text{ for } FANIN \ge 4$$

(14)

and the number of gates is given by

$$G3(N) = 12 \times N \text{ with } FANIN \ge 4.$$

(15)

| A | В. | <u>C</u> | PC_ | PS |

|---|----|----------|-----|----|

| 0 | 0  | 0        | 0   | 0  |

| 0 | 0  | 1        | 0   | 1  |

| 0 | 1  | 0        | 0   | 1  |

| 0 | 1  | 1        | 1   | 0  |

| 1 | 0  | 0        | 0   | 1  |

| 1 | 0  | 1        | 1   | 0  |

| 1 | 1  | 0        | 1   | 0  |

| 1 | 1  | 1        | 1   | 1  |

Table 1. Truth table for carry-save adder.

#### Multi-operand carry-save adder

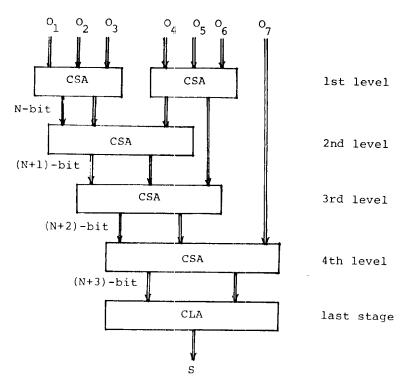

We now consider a 3-to-2 array sometimes called a Wallace adder tree as shown in Figure 11. Let I32(P,i) be the number of input operands to the ith level and let J32(P,i) be the number of CSA groups required at the ith level. It follows that

$$I32(P,i) = J32(P,i-1)x2+I32(P,i-1)-J32(P,i-1)x3$$

(16)

with

$$I32(P,1) = P.$$

$$J32(P,i) = [I32(P,i)/3]$$

(17)

The total number of CSA groups is

$$U3 = P-2$$

(18)

```

\nabla Z+TIME21 P;I

[1]

A THE NUMBER OF GATE-DELAYS FOR MULTIPLE OPERAND ADDITION

OF TWO-TO-ONE TREE STRUCTURE

[2]

A WORDS LENGTH N, FANIN ARE DEFINED EXTERNALLY

[3]

[4]

[5]

Z \leftarrow 0

[6]

Z \leftarrow Z + DELAYNUM N + I

[7]

\rightarrow (0 \leq I \leftarrow I \sim 1)/6

\nabla Z+CLA21 P;I;J

[1]

A THE NUMBER OF UNITS FOR MULTIPLE OPERAND ADDITION

OF TWO-TO-ONE TREE STRUCTURE

[2]

[3]

A WORD LENGTH N, FANIN ARE DEFINED EXTERNALLY

[4]

Z \leftarrow I \leftarrow 0

J+∟P ÷ 2

[5]

[6]

Z+Z+J\times UNIT N+I

[7]

P \leftarrow J + P - J \times 2

[8]

I+I+1

[9]

\rightarrow (P>1)/5

\nabla Z+GATE21 P; I; J

[1]

A THE NUMBER OF GATES FOR MULTIPLE OPERAND ADDITION

[2]

А

OF TWO-TO-ONE TREE STRUCTURE

[3]

A WORDS LENGTH N, FANIN ARE DEFINED EXTERNALLY

[4]

Z \leftarrow I \leftarrow 0

[5]

J \leftarrow LP \div 2

[6]

Z \leftarrow Z + J \times NUMGATE N + I

[7]

P \leftarrow J + P - J \times 2

[8]

I \leftarrow I + 1

[9]

\rightarrow (P>1)/5

```

Figure 9. Listing of APL functions TIME21, CLA21, and GATE21.

Figure 10. One position of a carry-save adder.

Figure 11. Example of 3-to-2 tree for P=7.

The number of levels of CSA required, L3(P), is computed iteratively as described by the APL function LEVEL32 in Figure 12.

$T4(N,FANIN,P) = T1(L1(FANIN,N+L3))+T3(FANIN)\timesL3(P)$ .

(19)

The number of CSA units required is

$$U4(N,FANIN,P) = \sum_{i=1}^{L3(P)} J32(P,i) \times (N+i-1).$$

(20)

The total number of gates required, including the N+L3 bit carry-lookahead adder at the output end of the tree, is given by

$G4(N,FANIN,P) = G2(N+L3,FANIN)+G3(N)\timesU4(N,FANIN,P)$ .

(21)

Figure 12 is a listing of the APL functions which compute L3, T4, U4, G4. These functions are denoted LEVEL32, TIME32, CSA32, and GATE32, respectively.

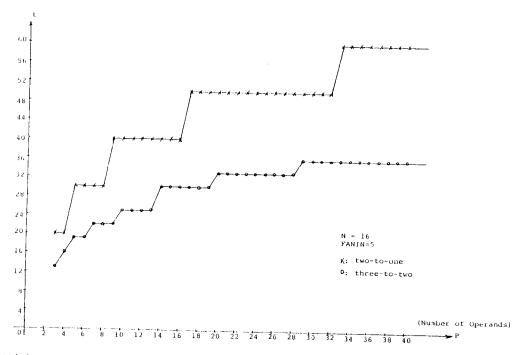

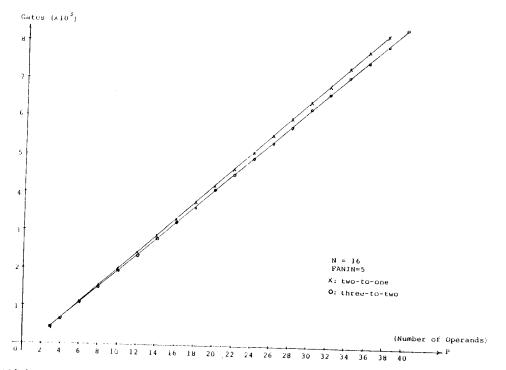

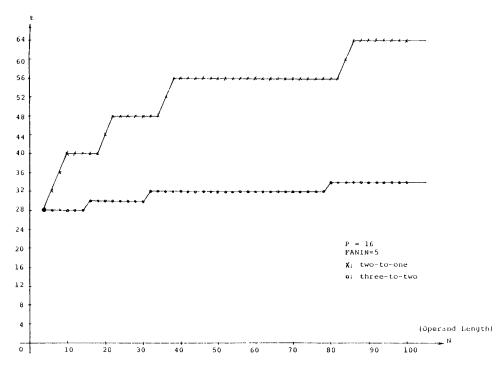

# NUMERICAL EVALUATION AND COMPARISON OF COST/PERFORMANCE FUNCTIONS

Our ultimate concern is with comparison of two pairs of functions of three variables, namely T2", G2", T4 and G4. Our approach has been to evaluate numerical examples and attempt to draw general conclusions. Figure 13 (a and b) shows a comparison of the two methods for fixed operand length and fan-in. In this case the 3-to-2 structure exhibits greater speed with lower gate count. Figure 14 (a and b) compares the structures with fixed values of P and FANIN as N, the operand length, varies. Here the 3-to-2 case is always faster but requires slightly more gates for N<14.

Tables 2 and 3 display some conclusions from trial computations. For FANIN values of 3 through 9, Table 2 lists the lower bound on N such that the time delay and gate count are smaller for the 3-to-2 structures than the 2-to-1 structures for any P in the range  $3 \le P \le 40$ . For example, if FANIN = 8, then for operand lengths of 10 bits or more, a carry-save adder tree is faster and requires fewer gates than a tree of carry-lookahead adders. If

```

\nabla Z+LEVEL32 P; J

[1]

M THE NUMBER OF LEVELS FOR THREE-TO-TWO TREE STRUCTURE

[2]

Z \leftarrow 0

[3]

\rightarrow (P \le 2)/0

[4]

J+LP÷3

[5]

P \leftarrow (J \times 2) + P - J \times 3

[6]

Z \leftarrow Z + 1

[7]

+3

\nabla Z+TIME32 P; I

Γ1<sup>7</sup>

A THE NUMBER OF GATE-DELAYS FOR MULTIPLE OPERAND ADDITION

A OF THREE-TO-TWO TREE STRUCTURE

N WORDS LENGTH N, FANIN AND CSAT ARE DEFINED EXTERNALLY

[4]

I+LEVEL32 P

[5]

Z \leftarrow (CSAT \times I) + DELAYNUM N + I

∇ Z+CSA32 P;I;J

A THE NUMBER OF CARRY SAVE ADDERS FOR MULTIPLE OPERAND

A ADDITION OF THREE-TO-TWO TREE STRUCTURE

[2]

[3]

Z \leftarrow I \leftarrow 0

[4]

\rightarrow (P \le 2)/0

[5]

J+ LP ÷ 3

[6]

Z \leftarrow Z + J \times N + I

[7]

P \leftarrow (J \times 2) + P - J \times 3

[8]

I \leftarrow I + 1

[9]

→4

\nabla Z+GATE32 P

A THE NUMBER OF GATES FOR MULTIPLE OPERAND ADDITION

[2]

OF THREE-TO-TWO TREE STRUCTURE

[3]

A WORDS LENGTH N, FANIN AND CSAC ARE DEFINED EXTERNALLY

[4]

Z+(CSAG×CSA32 P)+NUMGATE N+LEVEL32 P

```

Figure 12. Listing of APL functions LEVEL32, TIME32, CSA32, and GATE32.

N = 9 the delay is less but the gate count may not be. If N is less than 8 we cannot make a general statement about the relative cost and performance, but of course these could be computed for specific choices of N, P, and FANIN.

Table 3 lists the lower bound on P such that the time delay and gate count are smaller for the 3-to-2 structures that the 2-to-1 structures. Again if P is less than the bound, we cannot make a general statement.

## COST COMPARISONS UNDER PACKAGING CONSTRAINTS

Our measure of cost or complexity has so far been in terms of number of gates assuming a given limit of fan-in. One of our reasons for concentrating on structures based upon carry-lookahead and carry-save addsers was the fact that off-the-shelf integrated circuit components are available to implement these devices. At this point we revise of cost measure to be the number of circuit packages required under various restrictions on pin-outs.

It requires NUMBIT x 3+2 pins for each CL unit and 5 pins for each CSA unit and therefore

(PIN - 2)

$$\geq$$

H1 x (NUMBIT x 3 + 2) for CLA and, (22)

$$(PIN - 2) \ge H2 \times 5$$

for CSA, (23)

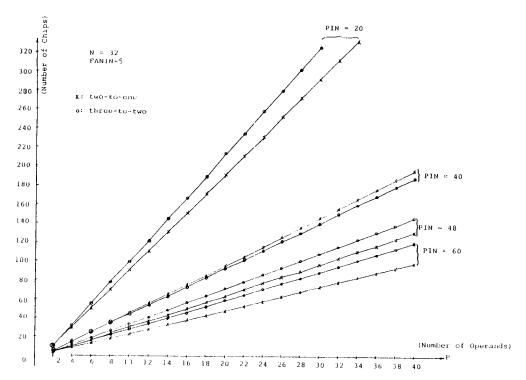

where H1 and H2 are the number of CLA and CSA units per package (chips) with PIN external connections. Two pins are assumed to be used for power and ground. Figure 15 is an APL function to calculate the number of chips required for both the CLA and CSA based schemes under restrictions of gate fan-in and package pin-outs. Figure 16 depicts some results from this function. Figure 17 summaries results from multiple evaluations of of the function CHIP. Notice that for a given value of FANIN (a column in Figure 17), the chip count for the 3-to-2 schemes are the smallest for larger values of N. In general the CSA structures do not appear to offer advantage over the CLA structures for as many choices of design parameters when we add the packaging restriction.

Figure 13(a). Operational delay vs. number of operands for 2-to-1 and 3-to-2 structures with N=16, FANIN=5.

Figure 13(b). Required number of gates vs. number of operands for 2-to-1 and 3-to-2 structures with N=16, FANIN=5.

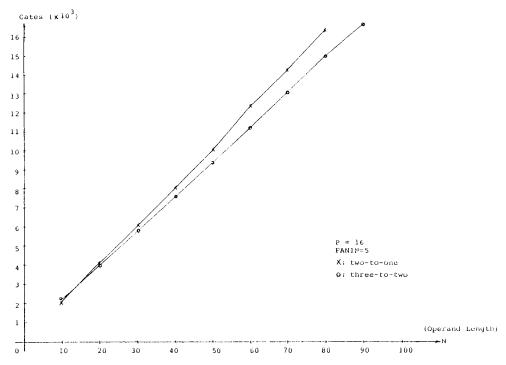

Figure 14(a). Operational delay vs. operand length for 2-to-1 and 3-to-2 structures with P=16 and FANIN=5.

Figure 14(b). Required number of gates vs. operand length for 2-to-1 and 3-to-2 structures with P=16 and FANIN=5.

```

\nabla Z+CHIP P; DEN; CL21; CL32; CS32; C32

A THE NUMBER OF LSI/MSI CHIPS FOR MULTIPLE OPERAND ADDITION OF TWO-TO-ONE AND THREE-TO-TWO TREE STRUCTURE

[1]

[2]

[3]

A WORD LENGTH N, FANIN, PIN ARE DEFINED EXTERNALLY

[4]

DEN+L(PIN-2) \div 2 + NUMBIT \times 3

[5]

\rightarrow (0 = DEN)/16

[6]

CL21+\Gamma(CLA21 P) \div DEN

CL32+\lceil (CLA32 P) \div DEN

[7]

CS32+[(CSA32 P)+[(PIN-2)+5

[8]

[9]

C32+CL32+CS32

[10]

'CHIPCLA21: ';CL21

[11]

[12]

';CL32

'CHIPCLA32:

[13]

'CHIPCSA32:

'CHIP32:

1;032

[14]

[15]

+0

[16]

'FAN IN IS TOO LARGE'

```

Figure 15. Listing of APL function CHIP.

Figure 16. Number of required packages vs. number of operands and pinouts for 2-to-1 and 3-to-2 structures with N=32 and FANIN=5.

| T.3 | 27 | ~ | NT. |  |

|-----|----|---|-----|--|

|     |    |   |     |  |

|     |    |   |     |  |

| OPERAND<br>LENGTH<br>8<br>16<br>32<br>64 | 3 4 5 6 7 8 9<br>L L L L X X X<br>L S L L X X X<br>S S L L X X X<br>S S L L X X X | PIN=20 |

|------------------------------------------|-----------------------------------------------------------------------------------|--------|

| 8<br>16<br>32<br>64                      | L L L L L L L L                                                                   | PIN=40 |

| 8<br>16<br>32<br>64                      | L L L L L L L L L L L L L L L L L L L                                             | PIN=48 |

| 8<br>16<br>32<br>64                      |                                                                                   | PIN=60 |

$\ensuremath{\mathsf{L}}$  denotes that the carry-Lookahead scheme  $\ensuremath{\mathsf{requires}}$  fewer chips.

S denotes that the carry-Save scheme requires fewer chips.

? Denotes that the relative costs cross over depending upon  ${\tt P.}$

X indicates that the gate fan-in is limited by number of package connections.

Figure 17. Comparison of package counts for 3-to-2 versus 2-to-1 schemes under fanin and package connection constraints.

| FANIN | TIME-DELAY      | GATES         |

|-------|-----------------|---------------|

| 3     | N≥5             | N≥51          |

| 71    | N <u>&gt;</u> 4 | N>24          |

| 5     | N≥5             | N <u>≥</u> 14 |

| 6     | N <u>≥</u> 6    | N <u>≥</u> 17 |

| 7     | N <u>≥</u> 7    | N <u>≥</u> 14 |

| 8     | N <u>&gt;</u> 8 | N <u>≥</u> 10 |

| 9     | N <u>≥</u> 9    | N <u>≥</u> 10 |

Table 2. Operand length such that 3-to-2 scheme is faster and/or requires fewer gates than 2-to-1 ( $4\le N\le 64$ ,  $3\le P\le 40$ ).

| FANIN | TIME-DELAY       | GATES            |

|-------|------------------|------------------|

| 3     | P>9              | _                |

| 4     | P <u>&gt;</u> 3  | -                |

| 5     | P≥5              | -                |

| 6     | P <u>≥</u> 9     | _                |

| 7     | P <u>&gt;</u> 17 | -                |

| 8     | P <u>&gt;</u> 33 | P <u>&gt;</u> 21 |

| 9     | P≥33             | P≥9              |

"-" denotes that the 3-to-2 case may not require less gates.

Table 3. Number of operands such that 3-to-2 scheme is faster and/or requires fewer gates than 2-to-1 ( $4\le N\le 64$ ,  $3\le P\le 40$ ).

#### REFERENCES

- B.K. Gilbert, et. al., "Ultra high speed transaxial image reconstruction of the heart, lungs, and circulation via numerical approximation methods and optimized processor architecture," accepted for publication in Computers and Biomedical Research.

- R. O. Berg and L. C. Kinney, "Serial adders with overflow correction", <u>IEEE Trans.</u> <u>Comp.</u>, vol. C-20, pp. 668-671, June 1971.

- A. Svoboba, "Adder with distributed control", <u>IEEE Trans. Comp.</u>, vol. C-19, pp. 749-751, Aug. 1970.

- 4. H. L. Garner, "Number systems and arithmetic", <u>Advances in Computers</u>, F. L. Alt and M. Rubinoff (ed.), vol. 6, Academic Press, pp. 131-194, 1965.

- A. J. Atrubin, "A one-dimensional real-time iterative multiplier", IEEE Trans. Electron. Comput., vol. EC-14, pp. 394-399, June 1965.

- O. L. MacSorley, "High speed arithmetic in binary computers", <u>Proc. IRE</u>, vol. 49, pp. 67-91, Jan. 1961.

- N. G. Kingsburg, "High speed binary multiplier", <u>Electron. Lett.</u>, vol. 7, pp. 277-278, May 20, 1971.

- 8. D. J. Kuck, <u>The Structure of Computers and Computations</u>, vol. I, class notes (to be scon published as a text), Department of Computer Science, University of Illinois, Urbana, Illinois.

- 9. C. S. Wallace, "A suggestion for a fast multiplier", IEEE Trans. Electron. Comput., vol. EC-13, pp. 14-17, Feb. 1964.

- 10. L. Dadda, "Some schemes for parallel multipliers", <u>Alta Freq.</u>, vol. 34, pp. 349-356, May 1965.

- L. Dadda and D. Ferrari, "Digital multipliers a unified approach", <u>Alta Freq.</u>, vol. 37, pp. 1079-1086, Nov. 1968.

- 12. J. A. Gibson and R. W. Gibbard, "Synthesis and comparison of two's complement parallel multipliers", <u>IEEE Trans.</u> <u>Comp.</u>, vol. C-24, pp. 1020-1027, Oct. 1975.

- J. C. Majithia and R. Kitai, "An iterative array for multiplication of signed binary numbers", <u>IEEE Trans. Comp.</u>, vol. C-20, pp. 214-216, Feb. 1971.

- S. D. Pezaris, "A 40-ns 17-bit by 17-bit array multiplier", <u>IEEE Trans. Comp.</u>, vol. C-20, pp. 442-447, April 1971.

- 15. A. Habibi and P. A. Wintz, "Fast multipliers", IEEE Trans. Comp., vol. C-19, pp. 153-157, Feb. 1970.

- 16. W. J. Stenzel, W. J. Kubitz and G. H. Garcia, "A compact high-speed parallel multiplication scheme", <u>IEEE Trans. Comp.</u>, vol. C-26, pp. 948-957, Oct. 1977.

- 17. I. T. Ho and T. C. Chen, "Multiple addition by residue threshold functions and their representation by array logic", IEEE Trans. Comp., vol. C-22, pp. 762-767, Aug. 1973.

- 18. N. Kouvaras, D. Lagoyannis and L. Ponticopoulos, "A digital system of simultaneous addition of several binary numbers", <u>IEEE Trans. Comp.</u>, vol. C-17, pp. 992-997, Oct. 1968.

- 19. E. E. Swartzlander, "The quasi-serial multiplier", <u>IEEE Trans. Comp.</u>, vol. C-22, pp. 317-321, April 1973.

- 20. E. E. Swartzlander, "Parallel counters", <u>IEEE Trans. Comp.</u>, vol. C-22, pp. 1021-1024, Nov. 1973.

- S. Singh and R. Waxman, "Multiple operand addition and multiplication", <u>IEEE Trans.</u> <u>Comp.</u>, vol. C-22, pp. 113-120, Feb. 1973.

- 22. D. E. Atkins, "A suggested approach to computer arithmetic for designers of multivalued logic processors", <u>Proceedings of the 8th International Symposium on Multi-Valued Logic</u>, IEEE No. 78 CH1366-4C, May 1978.

- 23. F.J. Hill and G.R. Peterson, <u>Digital Systems:</u>

<u>Hardware Organization and Design</u>, Chp. 11,

John Wiley and Sons, N.Y., 1973.

- G.A. Blaauw, <u>Digital system implementation</u>, Chp.2. Prentice-Hall, 1976.

- 25. J.R. Armstrong, "The efficient single output (d,r) circuit," <u>Proceedings of Eighth Annual Southeastern Symposium on System Theory</u>, pp. 63-66, April 1976.

- 26. J.E. Robertson, "A deterministic procedure for the design of carry-save adders and borrowsave subtracters," Department of Computer Science Report No. 235, University of Illinois, Urbana, July 1967.