# Parallel Adders Using Standard PLAs

#### Arnold Weinberger

International Business Machines Corporation B89/707, PO Box 390 Poughkeepsie, New York 12602

### ABSTRACT

PLA adders are described that add in one cycle and require a reasonable number of product terms for an 8, 16, or even a 32-bit adder. A procedure is also described for minimizing the number of product terms for any size adder.

# INDEX TERMS

Programmable Logic Array (PLA), input decoders, output exclusive-ORs, product term minimization, adder, carry-look-ahead.

## INTRODUCTION

Programmable Logic Arrays (PLAs) [1] have been successfully applied to control logic and simple functions, such as counters, small adders, etc. Large adders have usually been implemented on standard PLAs iteratively, a few bits per cycle. To implement a large adder in one cycle required too many product terms to be economical.

This paper describes single-cycle adder designs for standard PLAs that minimize the number of product terms to acceptable levels even for 16 and 32-bit adders. The PLAs have two features that reduce the number of product terms:

- 2-bit input decoders, where a pair of inputs and their inverters are replaced by a 2-input decoder and

- exclusive-OR(XOR) outputs, where a pair of OR array outputs are XORed.

The adder equations are expressed in a manner to take advantage of the two features and of various methods of sharing product terms. In particular, a string of several adjacent sum bits are expressed in terms of the carry into the string, using carry-look-ahead. A procedure is developed to optimize string sizes to further reduce the number of product terms.

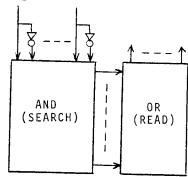

#### PLAs

A PLA consists basically of two arrays in series, an AND array and an OR array, as shown in Figure 1. The array names, AND-OR, describe the generic logic levels of the SEARCH-READ arrays of an associative table [2]. The two arrays may be implemented with other types of logic besides AND-OR. A widely-used logic is NOR-NOR implemented with MOS technology.

Figure 1. PLA (Programmable Logic Array)

The generic AND (SEARCH) array produces an array of product terms of the inputs to the PLA. Each product term is the AND of the inputs, as in (1). Each input enters the AND

Product Term=

$$f1(A) \cdot f2(B) \cdot ...$$

(1)

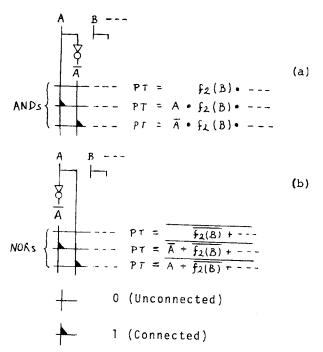

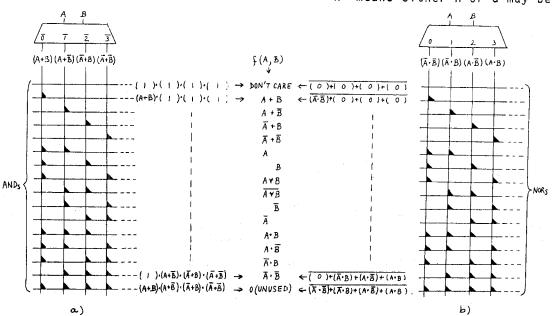

in one of three states: true, complement, or don't care. The true and complement lines of an input intersect the AND array at each AND with two bits which are personalized for one of the three states. The personalization is shown in Figure 2a when the generic AND (SEARCH word) is implemented with a real AND and in Figure 2b when implemented with a NOR.

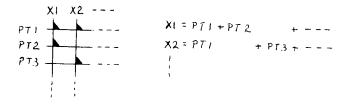

The generic OR (READ) array produces a generic OR of selected product terms on each array output. The array is personalized with a single bit at each intersection of a product term with an output line. A 1 selects the product term, a 0 does not. Each array output

is the real OR of selected product terms if the array is comprised of real ORs, as in Figure 3. If the array is comprised of NORs, each output is the NOR of selected product terms.

Figure 2. Personalization of AND (SEARCH) Array Using (a) Real ANDs or (b) NORs

Figure 3. Personalization of OR(READ) Array

It is well known that a function of n variables can be expressed as a sum of a subset of the minterms (or as a product of a subset of maxterms). There are  $2^n$  minterms (or maxterms) and therefore  $2^{2n}$  possible subsets of minterms (or maxterms).

A complete set of minterms (maxterms) corresponds to the positive (negative) outputs of an n-bit decoder. Figures 2a and b can be interpreted as providing a 1-bit decoder for input A: Figure 2a provides the two maxterms A and  $\overline{A}$ , while Figure 2b provides the corresponding two minterms  $\overline{A}$  and A.

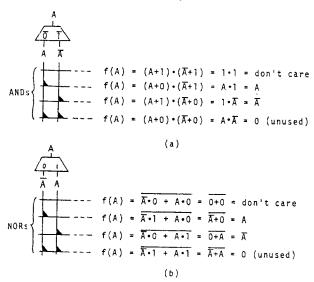

The personalized 2-bit cell at the intersection of a product term with the 1-bit decoder outputs corresponds to selecting the subset of minterms (maxterms) to comprise the desired function. Figure 4 shows the four possible functions of input A, of which three are used. Figure 4a shows the possible products of maxterms, each maxterm included or not according to the function to be personalized. A 1 is ORed with the maxterm if it is not included in the function, while a 0 is ORed if it is included. Similarly, Figure 4b shows the possible sums of minterms, each minterm included according to the function to be personalized. A 1 is ANDed with the minterm if included, a 0 if not. The complement of the OR function of A is actually shown, to correspond to the true function for a generic AND when implemented with a NOR.

Figure 4. One-input functions using a 1-input decoder and a personalized 2-bit cell with (a) complement decode outputs and maxterm personalization or (b) true decode outputs and minterm personalization.

The number of product terms is significantly reduced by substituting 2-bit decoders for a pair of 1-bit decoders [3]. The total number of decoder outputs remains the same. The product term now represents the AND of functions of pairs of inputs, as in (2).

Figure 5 shows the 16 possible functions of inputs A and B, of which 15 may be used. Figure 5a shows the possible

products of maxterms, while Figure 5b shows the possible sums of minterms. The latter defines functions of A and B to correspond to a NOR implementation of a product term, as in (3).

Product Term= fl(Al,Bl)+f2(A2,B2)+... (3)

This corresponds to Figure 4b for 1-bit decoders.

Two-input decoders have already been applied to a standard PLA [4] and will be shown to be particularly useful for adders.

Another economizing PLA feature is using XOR outputs [5]. Pairs of OR array outputs are XORed to produce a single PLA output.

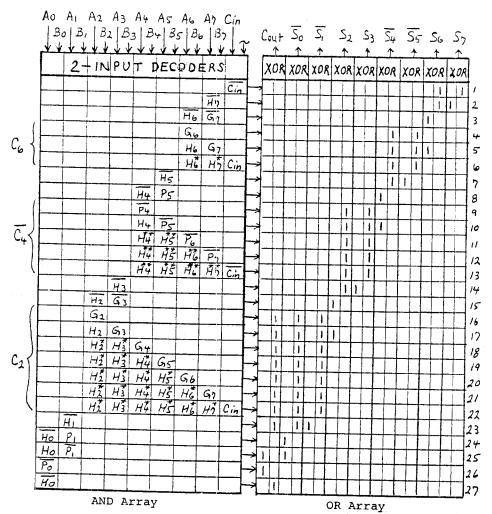

Figure 6 shows the PLA expanded to include 2-input decoders and XOR outputs.

### Adders

A typical adder adds two n-bit numbers,  $A(A_0,\ldots,A_{n-1})$  and  $B(B_0,\ldots,B_{n-1})$  together with an input carry Cin to produce a sum  $S(S_0,\ldots,S_{n-1})$  and an output carry Cout(=C $_0$ ). Using single-bit-position functions:

$G_i = A_i \bullet B_i$ ,  $P_i = A_i + B_i$ ,  $H_i = A_i \lor B_i$ , a carry from any bit position can be expressed directly in terms of single-b bit-position functions and the Cin, as in (4) and (5).

Figure 6. PLA with 2-Input Decoders and XOR Outputs

$$C_{i} = G_{i}$$

$$+H_{i}^{*} \cdot G_{i+1}$$

$$+H_{i}^{*} \cdot \dots \cdot H_{n-2}^{*} \cdot G_{n-1}$$

$$+H_{i}^{*} \cdot \dots \cdot H_{n-1}^{*} \cdot C_{in}$$

(4)

$$\overline{C}_{i} = \overline{P}_{i} + H_{i}^{**} \cdot \overline{P}_{i+1}$$

$$+ H_{i}^{**} \cdot \dots \cdot H_{n-2}^{**} \cdot \overline{P}_{n-1} + H_{i}^{**} \cdot \dots \cdot H_{n-1}^{**} \cdot \overline{C}_{in}$$

(5)

where  $H^*$  means either H or P may be used  $H^{**}$  means either H or  $\overline{G}$  may be used

Figure 5. Two-input functions using a 2-bit decoder and a personalized 4-bit cell with (a) complement decode outputs and maxterm personalization or (b) true decode outputs and minterm minimization.

Also, a sum bit can be expressed as a function of the output carry from the preceding bit position and expanded into an XOR of two entities, one of which includes a distant carry, as in (6) and (7).

$$S_{i} = H_{i} + C_{i+1} = H_{i} + (G_{i+1}^{j} + H_{i+1}^{j} \cdot C_{j+1})$$

$$= (H_{i} + G_{i+1}^{j}) + (H_{i+1}^{j} \cdot C_{j+1})$$

$$= (H_{i} + G_{i+1}^{j}) + (H_{i+1}^{j} + C_{j+1})$$

(6)

$$\overline{S}_{i} = H_{i} \Psi \overline{C}_{i+1} = H_{i} \Psi (\overline{GH}_{i+1}^{j} + H_{i+1}^{j} \cdot \overline{C}_{j+1})

= (H_{i} \Psi \overline{GH}_{i+1}^{j}) \Psi (H_{i+1}^{j} \cdot \overline{C}_{j+1})

= (H_{i} \Psi GH_{i+1}^{j}) \Psi (\overline{H}_{i+1} + C_{j+1})$$

(7)

$H_{i+1}^{j}$  = strict carry-propagate condition (mutually exclusive with  $G_{i+1}^{j}$ )

$GH_{i+1}^{j} = G_{i+1}^{j} + H_{i+1}^{j} = \text{inclusive carry-}$ propagate condition

$$G_{i+1}^{j} = G_{i+1}^{+H} * G_{i+2}^{+H} * G_{i+2}^{+H} * G_{i+1}^{+H} * G_{i+$$

$$H_{i+1}^{j} = H_{i+1} \cdot \dots \cdot H_{j}$$

$$\overline{H}_{i+1}^{j} = \overline{H}_{i+1} + \dots + \overline{H}_{j}$$

$$GH_{i+1}^{j} = G_{i+1}$$

$$+H_{i+1}^{*} \cdot G_{i+2}$$

$$+H_{i+1}^{*} \cdot \cdots \cdot G_{j-1}$$

$$+H_{i+1}^{*} \cdot \cdots \cdot H_{j-1}^{*} \cdot P_{j}$$

$$\overline{GH}_{i+1}^{j} = \overline{P}_{i+1}$$

$$+H_{i+1}^{**} \cdot \overline{P}_{i+2}$$

$$+H_{i+1}^{**} \cdot \dots \cdot H_{j-1}^{**} \cdot \overline{P}_{j}$$

In a similar fashion, the output carry can also be expressed as an XOR of two entities, one of which includes a distant carry, as shown in (8) and (9).

$$Cout = \overline{GH_0^j + H_0^j \cdot \overline{C}_{j+1}} = \overline{GH_0^j + H_0^j \cdot \overline{C}_{j+1}}$$

$$= \{\overline{GH_0^j}\} + \{\overline{H_0^j + C_{j+1}}\}$$

(8)

$$\overline{\text{Cout}} = \overline{G_0^{j} + H_0^{j} \cdot C_{j+1}} = \overline{G_0^{j} + H_0^{j} \cdot C_{j+1}}$$

$$= \{G_0^{j}\} + \{\overline{H_0^{j}} + \overline{C_{j+1}}\}$$

(9)

Eqs. (6) through (9) can also be expressed as functions of the distant carry of opposite polarity. The selected forms of the equations provide greater opportunities for sharing product terms.

# PLA Adder Designs

The adder equations can now be applied to the PLA of Figure 6.

Addend and augend of the same bit position, Ai and Bi, enter a common decoder, so that the intersection of an AND with the decoder outputs can produce a function of Ai and Bi, i.e., Gi, Pi, Hi, or their complements. The input carry Cin enters as the sole input to a decoder. (For uniformity, a 2-input decoder will be provided for Cin with one input unused.)

Sums are generated in strings, each string as a function of a common carry into the string, using Eqs. (6) and (7). A positive string of sum bits is shown in (10), and a negative string in (11). The output carry of the string is generated as a sum of products according to (4) or (5). For the purpose of counting product terms, a string includes the sum bits and the output carry of the string. The output carry of one string serves as the input carry to the next higher string.

Three string types are identified: low-order, intermediate, and high-order.

A low-order string includes a product term representing the input carry Cin or Cin, the low order sum bits implemented according to (10) or (11), and the product terms representing the output carry of the string according to (4) or (5). The indexes (j-1, j) become (n-1, in). Note that the high order sum of the string Si shares some of its product terms with the output carry of the string Ci, and

$\overline{\text{Si}}$  shares product terms with  $\overline{\text{Ci}}$ . Therefore, it is advantageous to use the same polarity output carry from the string as the sum bits. Since the sum bits are a function of the opposite polarity input carry to the string, it is also advantageous to alternate polarities of strings. It should also be noted that when sharing product terms between Si and Ci (or  $\overline{\text{Si}}$  and  $\overline{\text{Ci}}$ ), the common factor Hi must be used and Pi (or  $\overline{\text{GI}}$ ) cannot be substituted for it, i.e., Hi\* (or Hi\*\*) does not apply.

The number of unique product terms needed for a low-order string of K sum bits and its output carry is: 1 for the input carry, 1+2+5+...+(2K-1) for the sum bits (noting that some product terms are shared, e.g., Hj), and 2 for the additional unique (non-shared) product terms comprising the output carry of the string. Eq. (12) expresses Tlow, the number of unique product terms of low-order string for K>1.

$$T_{low} = 1 + [1 + 2 + 5 + - - + (2K - 1)] + 2 = K^2 + 2$$

(12)

Eq. (12) also holds for K=1, when the low-order sum is generated according to (13) or (14).

$$S_{n-1} = H_{n-1} \cdot \overline{cin} + \overline{H_{n-1}} \cdot cin$$

(13)

$$\overline{S}_{n-1} = H_{n-1} \cdot Cin + \overline{H_{n-1}} \cdot \overline{Cin}$$

(14)

together with the opposite polarity output carry of this string,  $\overline{C_{n-1}} = \overline{P_{n-1}} + H_{n-1}$ .  $\overline{C_{in}}$ , or  $\overline{C_{h-1}} = \overline{C_{h-1}} + H_{n-1}$ .  $\overline{C_{in}}$ , respectively. The two product terms of  $S_{n-1}$  (or  $\overline{S_{n-1}}$ ) and the additional unique product term for  $\overline{C_{n-1}}$  (or  $\overline{C_{n-1}}$ ) add up to three unique product terms for a low-order string of one. If a low-order string of one is used, the next string is of the same polarity as the low-order sum in order to make use of the opposite polarity output carry of the low-order string.

An <u>intermediate string</u> uses the product terms of the output carry of the preceding string to generate the sum bits according to Eqs. (10) or (11). It also generates the output carry of the string according to (4) or (5), respectively.

The number of unique product terms for an intermediate string Ti of size K>1 is one less than for a low-order string because the input carry to the string has already been counted as part of the preceding string. The output carry of the string has additional product terms equal to L, the number of bit positions of lower-order than the string.

$$T_i = K^2 + 1 + L \text{ for } K > 1$$

= 3+L for K=1

A high-order string generates the high-order sum bits as for an intermediate string. However, the output carry of the string,  $C_0$ , is needed only as an output of the adder,  $C_0$ out, so that it can be generated as in (8) or (9) as a function of the input carry to the string. Here, product terms can be shared between  $C_0$ out and  $C_0$ or between  $C_0$ out or  $C_0$ out.

The number of unique product terms for the high-order string, Thigh, is the same as for an intermediate string without the factor L, since the output carry is a function of the input carry to the string.

$$T_{high} = K^2 + 1 \text{ for } K > 1$$

(16)

Figure 7 illustrates an 8-bit adder divided into four strings of 2 bits each. The strings have been optimized to further reduce the total number of product terms to 27. Table 1 expresses the 8-bit adder in equation form to correspond to the PLA format used.

# Optimizing Strings

Optimum string sizes are determined differently for the different string types. For the low-order string, it is determined by minimizing the normalized number of product terms needed for a string, i.e., by determining  $(T_{low}/K)$  min.

$$(T_{low}/K)min = [(K^2+2)/K]min$$

= 3 for K=1 or 2

In other words, a minimum low-order string is either 1 or 2 bits long.

For an intermediate string, the minimum normalized number of product terms,

$$(T_i/K)$$

min =  $[(K^2+1+L)/K]$ min for  $K>1$ ,

=  $(3+L)$  for  $K=1$ ,

is a function of L, the number of bits of lower-order than the string. Successive (higher-order) intermediate strings should therefore be increasing monotonically. We, therefore, determine the transition value of L, Lt, for which string sizes K and K+1 are equally efficient. The value of Lt for string sizes 1 and 2 is:

$$3+L_{t} = (5+L_{t})/2, \cdot \cdot \cdot L_{t} = -1$$

so that it is always more efficient to have an intermediate string size of 2 than of 1. To determine larger string size transition values,

$$(K^{2}+1+L_{t})/K = [(K+1)^{2}+1+L_{t}]/(K+1)$$

$$L_{t} = K^{2}+K-1 \text{ for } K>1$$

(18)

Table 2 shows various transition values.

TABLE 1. Equations for 8-Bit Adder

$$S_7 = \left\{ \overline{H}_7 \right\} + \left\{ \overline{c} \text{ in} \right\}$$

$$S_6 = \left\{ \overline{H}_6 \cdot \overline{G}_7 \right\} + \left\{ \overline{H}_7 + \overline{c} \text{ in} \right\}$$

$$C_6 = G_6 + H_6 \cdot G_7 +$$

$$S_{2} = \begin{cases} \overline{H}_{2} \cdot \overline{G}_{3} \\ + H_{2} \cdot G_{3} \end{cases} + \begin{cases} \overline{H}_{3} + \overline{C}_{4} \end{cases} C_{2} = G_{2} \\ + H_{2} \cdot G_{3} \\ + H_{2} \cdot H_{3} \cdot G_{4} \\ + H_{2} \cdot H_{3} \cdot H_{4} \cdot G_{5} \\ + H_{2} \cdot H_{3} \cdot H_{4} \cdot H_{5} \cdot G_{6} \\ + H_{2} \cdot H_{3} \cdot H_{4} \cdot H_{5} \cdot G_{7} \\ + H_{2} \cdot H_{3} \cdot H_{4} \cdot H_{5} \cdot H_{5} \cdot H_{6} \cdot H_{7} \cdot Cin \end{cases}$$

$$Cout = C_0 = \left\{ \begin{array}{c} \overline{P}_0 \\ + \overline{H}_0 \cdot \overline{P}_1 \end{array} \right\} \Psi \left\{ \overline{H}_0 + \overline{H}_1 + C_2 \right\}$$

H\* H or P may be used H\*\* H or  $\overline{G}$  may be used

TABLE 2. Transition Values for Optimum Intermediate String Sizes

$$\frac{\mathsf{K} \longrightarrow (\mathsf{K}+1)}{\mathsf{L}_{\mathsf{t}}} \begin{array}{|c|c|c|c|c|c|c|}\hline & 2 \longrightarrow 3 & 3 \longrightarrow 4 & 4 \longrightarrow 5 & --- \\\hline & 5 & & 11 & & 19 & --- \\\hline \end{array}$$

In other words, after 5 lower-order bit positions, the next string size is equally efficient at 2 or 3; after 11 lower-order bit postions, the next string size is equally efficient at 3 or 4; etc.

The change in transition values,  $\Delta L_{\mbox{\scriptsize t}}$  , in (19), shows that

$$\Delta L_{t} = L_{t}(K \longrightarrow K+1) - L_{t}(K-1 \longrightarrow K)$$

$$= (K^{2}+K-1) - [(K-1)^{2}+(K-1)-1] = 2K$$

a pair of equal intermediate string sizes (two K-1 sizes) are followed by a pair

next higher size (two K sizes) for optimum assignment of intermediate string sizes. In other words, a low-order string is followed by intermediate strings of a pair of two's, a pair of three's, etc.

An optimum high-order string is determined in relation to the other strings. First we note that if the high-order string is greater than (smaller than) the adjacent intermediate string by two or more, the combined number of product terms for the two strings can be reduced by reducing (increasing) the high-order string by one and increasing (reducing) the adjacent intermediate string by one.

This leads to the following procedure for assigning string sizes: We begin with a low-order string of two (the larger of the two optimal sizes), followed by pairs of strings of two, three, etc. If the bit positions of the adder are exhausted when the high-order string is equal to or one greater than the adjacent string, the first-pass string assignment is final. If the high-order string is exactly one less than the adjacent string, the high-order string is increased by one and the low-order string is reduced by one to yield a more optimum assignment. If the high-order string is at least two less than the adjacent string, the latter becomes the new high-order string and the former high-order string is deemed a remainder to be absorbed by the intermediate strings as follows: For each pair of equally-sized intermediate strings, the high order of the pair is increased by not more than one. We can arbitrarily choose the high-to-low order pairs for increasing an intermediate string by one.

Table 3 illustrates the procedure for assigning optimum strings. The assignment is not necessarily unique. For some adder sizes other optima are possible. For example, the 8-bit adder of Figure 7 can also be implemented with 27 product terms using string sizes 1, 2, 2, and 3, low-to-high order.

Tables 4a, b and c illustrate the relevant parameters for 8-bit, 16-bit and 32-bit adders, using 27, 74 and 211 product terms, respectively.

#### CONCLUSION

PLAs have been shown to be capable of economically implementing one-cycle multi-bit adders. Economy is achieved using a special adder algorithm which permits a large amount of product term sharing as well as efficient use of 2-input decoders and exclusive-OR outputs.

Figure 7. 8-Bit Adder

TABLE 3. Illustration of Procedure for Optimal String Assignment

| First-pass string assignment (Nos. are string sizes) | Final string assign-<br>ment |

|------------------------------------------------------|------------------------------|

| 54433222                                             |                              |

| 44433222                                             | no change                    |

| 34433222                                             | 44433221                     |

| 3433222                                              | 4433221                      |

| 24433222                                             | 4443322                      |

| Z433222                                              | 443322                       |

| <b>1</b> 44 <b>3</b> 3222                            | 4443222                      |

| <b>1</b> 433222                                      | 443222                       |

- + above numbers marks strings to be increased by one

- above numbers marks strings to be decreased by one

- / through numbers marks remainder to be

absorbed

TABLE 4. Number of product terms for a) 8-bit, b)-16-bit and c) 32-bit PLA adders

| 01 | 23 | 45 | 67 | Cin | Bit position                                            |

|----|----|----|----|-----|---------------------------------------------------------|

| 2  | 2  | 2  | 2  |     | <pre>←K(String size)<br/>←L(Number of lower-order</pre> |

| 5  | 9  | 7  | 6  |     | bit positions) T(Number of product terms)               |

27 Product terms

(a)

| 0123 | 456          | 789          | 11<br>01 | 11<br>23    | 11<br>45 | Cin |                                        |       |

|------|--------------|--------------|----------|-------------|----------|-----|----------------------------------------|-------|

| 17   | 3<br>9<br>19 | 3<br>6<br>16 | 2 4 9    | 2<br>2<br>7 | 2 - 6    |     | <b>←</b> Κ<br><b>←</b> L<br><b>←</b> T |       |

|      |              |              |          | 1           | l        | 74  | ) Product                              | terms |

(b)

| 01234             | 56789         | 11111<br>01234 | 1111<br>5678  | 1222<br>9012 | 222<br>345   | 22<br>67    | 22<br>89    | 33<br>01 | Cin |             |

|-------------------|---------------|----------------|---------------|--------------|--------------|-------------|-------------|----------|-----|-------------|

| 5<br>26           | 5<br>22<br>48 | 5<br>17<br>43  | 4<br>13<br>30 | 4<br>9<br>26 | 3<br>6<br>16 | 2<br>4<br>9 | 2<br>2<br>7 | 2 - 6    |     | K<br>L<br>T |

| (C) Product terms |               |                |               |              |              |             |             |          |     |             |

#### REFERENCES

- W.N. Carr and J.P. Mize,

"MOS/LSI Design and Application."

McGraw-Hill Book Co., INc., New York

1972.

- 2. M. Flinders, P.L. Gardner, J.F. Minshull, R.J. Llewelyn, "Functional Memory as a General Purpose System Technology," <u>IEEE Computer Group Conference</u>, June 1970, pp. 314-324.

- A. Weinberger "Functional Memory Using Multistate Associative Cells," U.S. Patent #3761902.

- 4. J.C. Logue, N.F. Brickman, F. Howley, J.W. Jones, W.W. Wu, "Hardware Implementation of a Small System in Programmable Logic Arrays,"

IBM Journal of Research and Development, Vol. 19, No. 2, March 1975, pp. 110-119.

- 5. J.W. Jones, "Array Logic Macros,"

IBM Journal of Research and Development,

Vol. 19, No. 2, March 1975, pp.

120-126.