# MULTIPLE ADDITION AND PARALLEL COUNTER IN GENERALIZED BINARY AND NEGABINARY SYSTEMS

#### L. Bhuyan and Dharma P. Agrawal

Electrical and Computer Engineering Wayne State University Detroit, MI 48202

### Abstract

This paper explores the possibility of utilizing counters for reducing the partial products generated from multiplication of two numbers represented in a generalized binary system. Algorithm for multioperand addition of Koren's generalized number system are worked out. A carry look-ahead adder is developed and hardware aspects of possible counters for this class of binary number system are discussed. Negabinary counters are also introduced in line with those proposed for binary multiplication by Stenzel et al.

### I. Introduction

In a binary multiplication, the complexity and time increase with increased number of bits. Generation of a matrix of partial products with subsequent reducton of the matrix by means of pseudo-adders has been looked into by several authors. Matrix generation and compression schemes are much faster for larger operands. Traditional forms of operand reduction scheme use full adders to reduce the matrix. Dadda introduced the notion of a (c,d) counter as a combina-torial network which receives c bits of equal weight as input and produces a corresponding d bit sum as output. This class of counters were extended recently by Stenzel et al.  $^{2}$  to include counters which receive columns from several successive radix positions of the input and their sum is produced by taking the corresponding weights into account. They have successively implemented a 24x24 bit multiplier incorporating ROMs as (5,5;4) table lookup counters. This class of counters gives rise to a compact, high speed and less expensive parallel multiplication scheme.

On the other hand, considerable amount of work has been done in different number systems and in deriving arithmetic algorithms for them. Because of the unique advantage of representing the positive and negative numbers without a sign bit, several authors have looked into the negative radix number systems. Sankar et al. described algorithms for basic arithmetic operations in negative base. Some simpler, faster and more general algorithms were also proposed for negative radix number systems. Yuen offered a new (8,-4,-2,1) representation for decimal numbers to sim-

plify the carry generation process in B.C.D. addition. Zohar has concluded that the negabinary system has irrefutable advantage over the conventional binary system in special applications such as digital filtering and signal processing in general. In a more recent presentation, Koren and Maliniak discussed a unified approach to a broad class of number systems, characterized by  $<\beta, \land>$  and successfully derived algorithms for different arithmetic operations.

In this paper, an approach has been made to look into possible reduction of partial products in multiplication of two numbers, represented by  $\langle 2, \wedge \rangle$  system. Algorithm for multioperand addition in  $\langle \beta, \wedge \rangle$  system is derived in Section II to make the process feasible. A carry look-ahead adder for  $\langle 2, \wedge \rangle$  system has been developed in Section III for fast addition of final two rows. Section IV discusses the possibility of a generalized binary counter and its hardware implications. Finally in section V, negabinary counters are presented in line with those presented in Ref. 2.

## II. Generalized Binary Number System

Koren and Maliniak suggested a generalized number system characterized by the pair < $\beta,\Lambda>$ , where  $\beta$  is a positive integer and  $\Lambda$  is a vector  $(\lambda_{n-1},\lambda_{n-2},\ldots,\lambda_0)$ ,  $\lambda_i\epsilon\{-1,+1\}$ . The algebraic value x of an n-tuple  $(x_{n-1},x_{n-2},\ldots x_0)$ ,  $x_i\epsilon\{0,1,\ldots,\beta-1\}$  is defined by

$$X = \sum_{i=0}^{n-1} \lambda_i x_i \beta^i$$

(1)

A generalized binary system is one for which  $\beta{=}2,~\lambda_1\varepsilon({-}1,{+}1),~x_1\varepsilon\{0,1\},~\Lambda=(1,1,\ldots,1)$  for binary;  $(1,{-}1,1,\ldots,{-}1,1)$  for negabinary;  $({-}1,1,1,\ldots,1)$  for 2's complement; and  $(1,{-}1,{-}1,1,\ldots,1,{-}1,{-}1,1)$  for 8,-4,-2,1 code as suggested by Yuen and so on.

We are primarily interested to show that the partial products generated by multiplying two <2,\rangle numbers can also be reduced by the counter methods.

# Algorithm for Multioperand Addition

Considering the ith column of m operands  $x_{\dot{1}}'s$  in radix  $\beta$  and carries  $c_{\dot{1}}'s$  and borrows  $b_{\dot{1}}'s$  from preceding columns,

or

$$z_{i} = \lambda_{i} \sum_{i} x_{i} + \sum_{i} - \sum_{i} b_{i}$$

(2)

$z_{i} = \lambda_{i} s_{i} + \beta (c_{i+1} - b_{i+1}) + \beta^{2} (c_{i+2} - b_{i+2})$

$+ \dots + \beta^{j} (c_{i+j} - b_{i+j})$  (3)

where,

j is the no. of carries or borrows from the ith column, and s, is the sum bit.

This is subject to the following condition,

$$\beta^{j+1} - 1 \ge \sum_{m} \beta + \sum_{i} c_{i}, \quad c_{i} \in \{0, 1, \dots, \beta-1\}$$

(4)

or,

$$j \geq \frac{\log(1+\Sigma\beta+\Sigma_{c_{1}})}{\log \beta} -1$$

(5)

Restricting the above equations to two carries or two borrows,

$$s_i = (\lambda_i z_i) \mod \beta$$

(6)

Case I

$$z_{i} \geq \lambda_{i} s_{i}$$

$$b_{i+1} = b_{i+2} = 0$$

$$c_{i+1} = (\frac{1}{\beta}(z_{i} - \lambda_{i} s_{i})) \mod \beta$$

$$c_{i+2} = \frac{1}{\beta^{2}}(z_{i} - \lambda_{i} s_{i}) - \frac{1}{\beta} c_{i+1}$$

(7)

### Case II

$$z_{i} < \lambda_{i} s_{i}$$

$$c_{i+1} = c_{i+2} = 0$$

$$b_{i+1} = (\frac{1}{\beta}(\lambda_{i} s_{i} - Z_{i})) \mod \beta$$

$$b_{i+2} = \frac{1}{\beta 2}(\lambda_{i} s_{i} - Z_{i}) + \frac{1}{\beta} b_{i+1}$$

(8)

For a generalized binary system with  $x = \sum_{i=0}^{n-1} \lambda_i x_i^2, \lambda_i \epsilon \{-1,+1\},$

$x_i \in \{0,1\}$  the above set of equations can be modified by substituting  $\beta=2$ .

# III. Carry Look Ahead Adder for <2, A> System

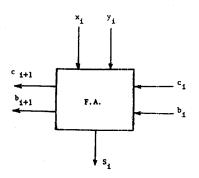

Reduction of two operands is usually done by the carry-look ahead adders  $^8$  and hence we consider the design of such adders for  $<2, \land>$  system. To do this, a full adder for two operands with one carry and one borrow inputs is given in Fig. 1a and n such full adders can be connected to give a n-bit parallel adder in  $<2, \land>$  system.

The logical expressions are given by 7,

$$\begin{aligned} \mathbf{s}_{i} &= \mathbf{x}_{i} \oplus \mathbf{y}_{i} \oplus (\mathbf{c}_{i} + \mathbf{b}_{i}) \\ \mathbf{c}_{i+1} &= \mathbf{y}_{i} (\mathbf{x}_{i} + \mathbf{y}_{i}) \mathbf{c}_{i} + \bar{\mathbf{y}}_{i} \bar{\mathbf{x}}_{i} \bar{\mathbf{y}}_{i} \mathbf{c}_{i} + \mathbf{y}_{i} \mathbf{x}_{i} \mathbf{y}_{i} \bar{\mathbf{b}}_{i} \\ \mathbf{b}_{i+1} &= \bar{\mathbf{y}}_{i} (\mathbf{x}_{i} + \mathbf{y}_{i}) \mathbf{b}_{i} + \mathbf{y}_{i} \bar{\mathbf{x}}_{i} \bar{\mathbf{y}}_{i} \mathbf{b}_{i} + \bar{\mathbf{y}}_{i} \mathbf{x}_{i} \mathbf{y}_{i} \bar{\mathbf{c}}_{i} \end{aligned}$$

where, x and y are two operands

and

$$\gamma_i = 0$$

for  $\lambda_i = -1$

=1 for  $\lambda_i = +1$

The above set of equations (9) is not valid for the case  $b_i = c_i = 1$  and the carries  $(\sqrt{})$  and borrows (x), generated are shown in Fig. 1b. These equations are also too complex and their implementation in the form of Carry Look Ahead Adder is extremely difficult.

In order to simplify the equations for a Carry Look Ahead Adder, the hypothetical case of  $b_i = c_i = 1$ , which is equivalent to  $b_i = c_i = 0$ , is introduced giving rise to an extra row in the K-map of Fig. 1b. Further simplification is obtained by introducing additional carry-borrow  $(\sqrt{x})$  null pairs and this leads to a complete K-map drawn in Fig. 1c. The following logical expressions are derived.

$$c_{i+1} = \bar{\gamma}_{i}\bar{x}_{i}\bar{y}_{i} + \gamma_{i}(x_{i}+y_{i}) = \gamma_{i}\overline{\theta(x_{i}+y_{i})} = p_{i} \quad (10)$$

$$b_{i+1} = (Q_{i}+\bar{c}_{i})b_{i} + Q_{i}\bar{c}_{i} \quad (11)$$

where

$$Q_i = \tilde{\gamma}_i (x_i y_i + \tilde{x}_i \tilde{y}_i) + \gamma_i (x_i \tilde{y}_i + \tilde{x}_i y_i)$$

$$= \overline{\gamma_i \cdot x_i \cdot y_i}$$

$$b_{i+1} = (Q_i + \bar{p}_{i-1})b_i + Q_i \bar{p}_{i-1}$$

$$= Q_i \bar{p}_{i-1} + (Q_i + \bar{p}_{i-1})b_i$$

(12)

and  $c_{i+1} = p_i$

In terms of the previous output,

$$b_{i+1} = Q_{i}\bar{p}_{i-1} + Q_{i-1}\bar{p}_{i-2}(Q_{i} + \bar{p}_{i-1}) + (Q_{i} + \bar{p}_{i-1})(Q_{i-1} + \bar{p}_{i-2})b_{i-1}$$

(13)

Expanding further,

$$b_{i+1} = Q_{i}\bar{p}_{i-1} + Q_{i-1}\bar{p}_{i-2}(Q_{i}+\bar{p}_{i-1})$$

$$+ Q_{i-2}\bar{p}_{i-3}(Q_{i}+\bar{p}_{i-1})(Q_{i-1}+\bar{p}_{i-2})$$

$$+ (Q_{i}+\bar{p}_{i-1})(Q_{i-1}+\bar{p}_{i-2}) \dots (Q_{1}+\bar{p}_{0})Q_{0}$$

$$b_{i}\bar{p}_{i} = Q_{i}\bar{p}_{i} = Q_{i}\bar{p}_{i} + Q_{i}\bar{p}_{i} + Q_{i}\bar{p}_{i} + Q_{i}\bar{p}_{i} = Q_{i}\bar{p}_{i} + Q_{i}\bar{p}_{$$

with

$$b_1 = Q_0$$

,  $c_1 = p_0$  for  $b_0 = c_0 = 0$  (14)

Hence, with the help of logic gates, eqn. (10) and (14) can be implemented to generate the carry and borrow inputs  $c_{i+1}$  and  $b_{i+1}$  to the (i+1)th column at a faster rate than would be expected out of an ordinary parallel adder using eqn. (9).

### IV. Generalized Binary Counter

For a (c,d) counter with c inputs and d outputs, the number of output bits must be sufficient to represent all possible sums of c bits, hence,

$$2^{d} - 1 \ge c$$

, for a n operand addition with  $(c-n)$  carries.

$$2^{d} - 1 \ge c$$

, for a n operand addition with

$$(c-n) \text{ carries.}$$

The outputz<sub>i</sub> =  $\sum_{j=1}^{d} c_{i+j} 2^{i+j} + s_{i}$  for  $\lambda_{i} = 1$  (15)

$$= -\sum_{j=1}^{d-1} b_{i+j} 2^{i+j} - s_{i} \quad \text{for } \lambda_{i} = -1$$

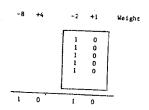

Obviously, for one addition, there have to be (d-1) carry outputs and (d-1) borrow outputs besides s for taking into consideration both  $\lambda_i$ =+1 or -1. Since carry and borrow outputs cannot occur simultaneously, they can be viewed as a single output for each column. Figure 2a shows a (7.3) counter giving rise to two carry outputs or two borrow outputs corresponding to  $\lambda_i = +1$  or -1respectively.

## A (5,5;4) Generalized Binary Counter

The idea of a (c;d) counter can as well be extended to counter of type  $(c_{k-1}, c_{k-2}, \dots, c_0; d)$ , where k is the number of successive input columns,  $\mathbf{c}_{\mathbf{i}}$  is the number of input bits in ith column corresponding to a weight  $2^{i}$  and d is the required number of output bits. The value of the output is

$$V = \sum_{i=0}^{k-1} \lambda_{i} \sum_{j=0}^{c_{i-1}} x_{ij} 2^{i}$$

(16)

and again subject to the condition that

$$2^{d}-1 \ge \sum_{i=0}^{k-1} c_{i} 2^{i}$$

(17)

A (5,5;4) counter is shown in Fig. 2b adding 5 inputs each at two successive columns and giving 2 sum outputs and 2 carry or borrow outputs for the next two bit positions.

In case of a (5,5;4) counter, the maximum

value occurs when both  $\lambda_i$ s are +1 and the minimum value occurs when both  $\lambda_i$ s are -1. Fig. 2c shows both the cases producing different carry and borrow outputs. It should be kept in mind that the carry output has to be added where as the borrow output has to be subtracted in the corresponding columns irrespective of the value of  $\lambda_i$ s.

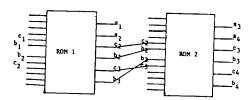

For a (5,5;4) counter of this type to be used in reduction of partial products, there have to be provision to take into account the extra outputs available from the previous counter. As carry and borrow outputs cannot occur simultaneously, this poses no problem to the usefulness of a counter. It is worth mentioning that either the carry or the borrow output of the counter will have the same sign as the corresponding input bits and hence, it can be treated as input bits. Thus, the number of inputs to the ROM is reduced to 5+5+2 for the two unaccounted carries/borrows. In otherwords, a 4K by 6 bits ROM can be used for a (5,5;4) counter with 12 inputs and 4+2=6 outputs. Again, to take into account four different combinations of  $\lambda_i^{}$ s, there have to be ROMs with four different types of contents to reflect the four possible combinations of the two successive  $\lambda_i$ s. This still seems to be quite expensive. However, keeping in view the complexity of the problem involved, this is quite expected. Fig. 3a shows the connection between two ROMs in the reduction of partial product matrix of very high number of operands. For the cases where  $c_1 < 5$  the ROMs have only 5+5=10 inputs and only one level of counters is necessary as shown in Fig. 3b. The last two columns can be added by using the carry look ahead adder developed in the preceding section.

## V. Negabinary Counters

The algorithm developed in 4 for multioperand addition in a negative base is reproduced in Table 1 for easy understanding.

Clearly, for negabinary system and for cases  $k > \beta = 2$ , the addition will generate more carries  $c_{i+3}$ ,  $c_{i+4}$ , etc. as the number of operand increases. We restrict our observations to  $k{\le}2\,,$  giving only twin carries. This results in a  $(c\,;d)$ counter where c=5 and d=3. +5 represented by 101 and +3 represented by 111.

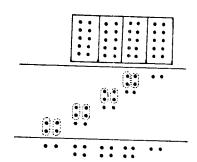

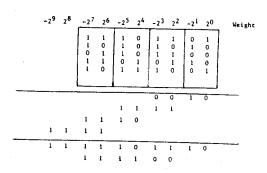

# A (5,5;4) negabinary counter

As suggested by Stenzel et al. for binary numbers, equal column counters can also be employed for reducing the negabinary partial products. Maximum efficiency is achieved by introducing (5,5;4) negabinary counters which reduces a matrix of 5 rows high to 2 rows high. The final two rows can be summed through negabinary carry look ahead (c.l.a.) adders<sup>8</sup> or modifed binary c.l.a. adders<sup>9</sup>. As an example of a (5,5;4) counter, fig. 4(a) shows the addition of 5 negabinary numbers of weight 1,-2 to produce a 4 bit output. The numbers involved are of maximum negative value representable in a 2 bit negabinary system. This also holds good for any two adjacent columns. Fig. 4(b) shows the reduction of an arbitrary 5 bit negabinary addition employing (5,5;4) counters. A generalized  $(c_{k-1},\ c_{k-2},\ \dots,\ c_0;d)$  type counter can also be worked out in a negabinary system, where k is the number of input columns,  $c_i$  is the number of input bits in the column of weight  $2^i$  and d is the number of bits in the output word. Table II verifies that (5,5;4), (4,5,5;5), (4,4,5,5;6), ..., etc. negabinary counters are possible as in the binary case.

A simple (5,5;4) negabinary counter can be implemented by 1K by 4 bit ROM with 10 address lines representing two columns of 5 bit inputs, as in the case of binary counters suggested by Stenzel et al., but the output of the ROM will be completely different.

# VI. Conclusion

The results presented in this paper provide a unified methodology for performing multiple addition and for implementing parallel counter when the numbers are represented in a generalized binary system. One special case of negabinary system is observed to require the same amount of hardware as needed by binary parallel counters and system looks to be attractive for special purpose applications.

### References

- L. Dadda, "Some schemes for parallel multipliers," Alta. Freq., Vol. 19, pp. 349-356, May 1965.

- W.J. Stenzel, W.J. Kubitz and G.H. Garcia, "A compact high speed parallel multiplication scheme," IEEE Trans. on Computers, Vol. C-26, pp. 948-957, Oct. 1977.

- P.V. Sankar, S. Chakravarti and E.V. Krishnamurty, "Arithmetic Algorithms in a Negative Base," IEEE Trans. on Computers, Vol. C-22, pp. 120-125, Feb. 1973.

- D.P. Agrawal, "Arithmetic Algorithms in a Negative Base," IEEE Trans. on Computers, Vol. C-24, pp. 998-1000, Oct. 1975.

- C.K. Yuen, "A new representation for decimal numbers," IEEE Trans. on Computers, Vol. C-26, pp. 1286-1288, Dec. 1977.

- S. Zohar, "New hardware realizations of recursive digital filters," IEEE Trans. on Computers, Vol. C-22, pp. 328-338, April 1973.

- I. Koren and Y. Maliniak, "A unified approach to a class of number systems," IEEE 4th Computer Arithmetic Symposium, Santa Monica, pp. 25-28, Oct. 1978.

- 8. D.P. Agrawal, "Negabinary Carry Look-Ahead Adder and Fast Multiplier," Electronic Letters, Vol. 10, pp. 312-313, July 25, 1974.

- D.P. Agrawal, "On Negabinary-Binary Arithmetic Relationships and their Hardware Reciprocity," IEEE Trans. of Computers, Vol. C-29, No. 11, pp. 1032-1035, Nov. 1980.

TABLE I

|         | $z_i = \sum_i x_i$                                                          | 3 i                   | c <sub>i+1</sub> | c <sub>i+2</sub> |

|---------|-----------------------------------------------------------------------------|-----------------------|------------------|------------------|

| Case I  | z <sub>i</sub> < β                                                          | ²i                    | 0                | 0                |

| Case II | (kβ≦z <sub>i</sub> <(k+1)β<br>for k=1,β                                     | (z <sub>i</sub> )modβ | β-k              | 1                |

| Case II | $(t\beta+k)\beta \le z_{1} < (t\beta+k+1)\beta$ for t=1,\beta-2 $k=1,\beta$ | (z <sub>i</sub> )modβ | β-k              | t+1              |

where,  $\beta\text{=}radix$ ,  $x_{i}^{\text{=}sum}$  bit,  $c_{i+2}^{\text{}}$  and  $c_{i+1}^{\text{}}$  are twin carriers.

Table II

| # of outputs | Possible<br>Absolute<br>Max Value                                | Possible<br>Absolute<br>Min Value                              | Limit of<br>Operands                                                                     | Counters<br>Type |

|--------------|------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------|

| 4            | $(-2)^{i+3} + (-2)^{i+1}$                                        | (-2) <sup>i+2</sup> +(-2) <sup>i</sup>                         | 5(-2) <sup>i+1</sup> ;5(-2) <sup>i</sup>                                                 | (5,5;4)          |

| 5            | (-2) <sup>i+4</sup> +(-2) <sup>i+2</sup><br>+(-2) <sup>i</sup>   | $(-2)^{i+3} + (-2)^{i+1}$                                      | 4(-2) <sup>i+2</sup> +5(-2) <sup>i</sup> ;<br>5(-2) <sup>i+1</sup>                       | (4,5,5;5)        |

| 6            | (-2) <sup>i+5</sup> +(-2) <sup>i+3</sup><br>+(-2) <sup>i+1</sup> | (-2) <sup>i+4</sup> +(-2) <sup>i+2</sup><br>+(-2) <sup>i</sup> | 4(-2) <sup>i+3</sup> +5(-2) <sup>i+1</sup> ;<br>4(-2) <sup>i+2</sup> +5(-2) <sup>i</sup> | (4,4,5,5;6)      |

Fig. la. A generalized binary Full Adder

| 7171 1120                     |          |    | ł          | ٧,٠ | Υ <sub>1</sub> =1 |    |    |    |

|-------------------------------|----------|----|------------|-----|-------------------|----|----|----|

| b <sub>i</sub> c <sub>i</sub> | 00       | 01 | 11         | 10  | 10                | 11 | 01 | 00 |

| 00                            | /x       |    | . <b>x</b> |     | /x                | 1  | √x |    |

| 01                            | <i>,</i> |    |            |     | 1                 | 1  | 1  |    |

| 11 .                          | √x       |    | ×          |     | /x                | 1  | √x |    |

| 10                            | √x       | ×  | ×          | x   | /x                | √x | √x | ×  |

|                               |          |    |            |     |                   |    |    |    |

√ - carries

x - borrows

Pig. 1c. Complete K-map for carry and borrow outputs.

| x                             | i <sup>y</sup> i | γ <sub>1</sub> = ( | )  |    | i  | Υį       | <b>-</b> 1 |    |

|-------------------------------|------------------|--------------------|----|----|----|----------|------------|----|

| b <sub>i</sub> c <sub>i</sub> | 00               | 01                 | 11 | 10 | 10 | 11       | 01         | 00 |

| 00                            |                  |                    | ×  |    |    | <b>*</b> |            |    |

| 01                            | 1                |                    |    |    | 1  | J        | 1          |    |

| 11                            |                  |                    |    |    |    |          |            |    |

| 10                            |                  | x                  | ×  | ×  |    |          |            | ×  |

√ - carries

x - borrow

Fig. 1b. Carry and borrow outputs from ith column

Fig. 2a. A (7,3) Generalized binary counter.

Fig. 2b. A (5,5,4) Generalized binary counter.

Fig. 2c. Maximum and minimum situations in a (5,5,4) counter.

Fig. 4a. A (5,5,4) negabinary counter.

Fig. 3a. Interconnection between ROMs.

Fig. 3b. Effect of adjoint counters.

Fig. 4b. Effect of adjoint negabinary counters.