# SIGN DETECTION IN THE SYMMETRIC RESIDUE NUMBER SYSTEM

Saroj Kaushik and R.K. Arora

Computer Centre, Indian Institute of Technology, Delhi New Delhi 110016, India

#### **ABSTRACT**

This paper is concerned with the algebraic sign detection of a number in the Symmetric Residue Number System. A new approach has been suggested which completely avoids the time consuming process of the Symmetric Mixed Radix Conversion (SMRC). An algorithm based on the above approach implementable in parallel for sign detection is also presented. The hardware representation of the above algorithm is shown. The time and hardware complexity required for the process have also been computed.

#### INTRODUCT ION

Several kinds of representation for residue numbers have been proposed, each of which has merits and demerits. The Symmetric Residue Number System (SRNS) has many advantages over the Residue Number System (RNS) viz., it is easy in the SRMS to find the additive inverse of a residue digit, it gives an effective solution for sign sensing and magnitude datermination etc. Many solutions to the problem of sign datection in the RMS have been suggested 4, but in the SRMS, there is no specific method for detecting the sign of a number except the SMMC process. Certainly it computes the sign but is relatively time consuming because of the cascaded process used. Besides, it furnishes more information (all symmetric mixed radix co-efficients). The purpose of this paper is to present a new approach for algebraic sign determination in the SRNS, which completely avoids the time consuming process of the SMRC.

# SYMMETRIC RESIDUE ARITHMETIC FUNDAMEN -TALS

Before considering the problem of sign detection, the basic definitions and operations in the SAMS are introduced to make this paper self-contained.

Definition 1: The symmetric residue of X modulo m is the least remainder in absolute value when an integer X is divided by another positive integer m. Here m is called a modulus. A commanly used form of this condition is

$$x = \left[\frac{x}{m}\right]^* \cdot m + /x/_m$$

,

where  $\left[-\frac{m}{2}\right]^{4}/x/m \leq \left[\frac{m}{2}\right]^{**}$ .

/X/m is the notation for symmetric residue of X with respect to m. When m is odd, these residues are symmetric with respect to the origin, but when m is even, perfect symmetry is lost. In this case, the quantity  $\frac{X}{m}$  is again the closest integer to  $\frac{X}{m}$ , except that if X is of the form  $\frac{Dm}{2}$ , where n is odd, then the quantity  $\frac{X}{m}$  is the closest integer to  $\frac{X-1}{m}$ .

Definition 2: The ordered n-tuple (/X/m<sub>1</sub>, /X/m<sub>2</sub>,...,/X/m<sub>n</sub>) of symmetric residues of X with respect to an ordered set (m<sub>1</sub>, m<sub>2</sub>,..., m<sub>n</sub>) of n moduli form the symmetric residue representation of X.

Definition 3: The SRMS is defined as a number system where the integers in the interval  $\begin{bmatrix} -\frac{m}{2} + 1, \frac{m}{2} \end{bmatrix}$  (upper square

brackets indicate a closed interval), where  $M = \iint_{i=1}^{\infty} m_i$ , are represented by

their symmetric residue representation corresponding to the moduli  $m_1, m_2, \cdots, m_n$ . If these moduli are chosen to be pairwise relatively prime, then any integer in the interval  $\begin{bmatrix} -\frac{M}{2} \end{bmatrix} + 1$ ,  $\begin{bmatrix} \frac{M}{2} \end{bmatrix}$  is uniquely

\* [1] denotes the closest integer to 1.

\*\*[I] denotes the floor of I i.e., the largest integer ∠ I.

represented by its symmetric residue representation and it is denoted by

$$X \longleftrightarrow (/X/_{m_1}, /X/_{m_2}, ..., /X/_{m_n}).$$

The addition, subtraction and multiplication of two numbers X and Y in the SRNS is defined as follows as long as the operands and the result are falling in the interval  $\begin{bmatrix} -\frac{M}{2} \end{bmatrix} + 1$ ,  $\begin{bmatrix} \frac{M}{2} \end{bmatrix}$ .

$$x*Y \longleftrightarrow (//x/_{m_1}*/Y/_{m_1}/_{m_1},//x/_{m_2}*/Y/_{m_2}/_{m_2},$$

...,  $//x/_{m_n}*/Y/_{m_n}/_{m_n})$

where the symbol \* represents addition, subtraction or multiplication of two numbers.

Symmetric Mixed Conversion Process: It is used to convert a residue code of a number to its symmetric mixed-radix representation. A number X may be expressed in symmetric mixed radix form as

$$x = r_n \prod_{i=1}^{n-1} m_i + \cdots + r_3 \cdot m_1 \cdot m_2 + r_2 \cdot m_1 + r_1,$$

(1)

where  $r_i$  and determined sequentially from equation (1).

# GENERAL APPROACH FOR SIGN DETECTION IN THE SRNS

We prove the following theorem based on which an algorithm has been suggested. An implementation of this algorithm has also been proposed which is parallel in nature. For the sake of simplicity, we write  $/X/_{mi} = x_i$ , i=1,2,..., n. Let  $\frac{A}{mi} = \frac{M}{m}$ .

### Theorem

For any modulus  $m_1$ ,  $1 \le i \le n$ , the sign of a number X in the interval  $\left[ \left[ -\frac{M}{2} \right] + 1, \left[ \frac{M}{2} \right] \right]$  is established by a proposition P in the following way: Case (a): If  $m_1$  is odd, then X is nonnegative iff

$$P = \begin{cases} \frac{\hat{m}_{i}}{2} \\ \hat{j} = 1 \end{cases} \begin{cases} x_{k} = /j \cdot m_{i} + x_{i} / m_{k} \end{cases}$$

$$V \begin{cases} x_{i} = /x_{i} / m_{k} \wedge x_{i} \ge 0 \end{cases}$$

is true for k= 1,2,..., i-1, i+1,..., n.

Case (b): If m is even, then X is non-negative iff

$$P = \sum_{j=1}^{\frac{m_{i}}{2}} -1$$

$$\{ \times_{k} = /j \cdot m_{i} + \times_{i} / m_{k} \}$$

$$\{ \times_{k} = / \lfloor \frac{m_{i}}{2} \rfloor \cdot m_{i} + \times_{i} / m_{k} \land \times_{i} \leq 0 \}$$

$$V\{x_k = /x_i/_{m_k} \land x_i \ge 0\}$$

is true

for k = 1, 2, ..., i-1, i+1, ..., n,

where  $\bigvee$ ,  $\bigwedge$  are logical 'OR' and 'AND' operators.

Proof: Proof is given in an appendix.

Remark 1: The number of iterations can be reduced by choosing m, to be the largest modulus.

# ALGORITHM FOR SIGN DETECTION OF A RESIDUE NUMBER

The following algorithm, based on the above theorem is used to detect the sign of a residue number. Choose  $m_i$  to be the largest modulus and let  $P = \frac{m_i}{2}$ .

# Algorithm

Input: The number  $X \leftrightarrow (x_1, x_2, ..., x_n)$ .

Output: The sign of X.

#### Procedure

Step 1: Start the processes  $Q_1$  and  $Q_2$  simultaneously:

$\mathbf{Q}_1$  and  $\mathbf{Q}_2$ : Obtain the symmetric residue representation of  $\mathbf{x}_i$  &  $\mathbf{m}_i^{\text{W-r-t}}$ .

$$x_i \leftrightarrow (x_i^1, x_i^2, \dots, x_i^{i-1}, x_i^{i+1}, \dots, x_i^n),$$

$$m_{i} \longleftrightarrow (m_{i}^{1}, m_{i}^{2}, \dots, m_{i}^{i-1}, m_{i}^{i+1}, \dots, m_{i}^{n}),$$

$$x_{1}^{j} = /x_{1}/m_{j}$$

and  $m_{1}^{j} = /m_{1}/m_{j}$ ,  $j=1,2,...$ ,

$i=1, i+1,...$  n.

Step 2: Start the processes R<sub>D</sub>, R<sub>1</sub>, R<sub>2</sub>,

...,R<sub>p</sub>,R<sub>p</sub>.

Comment - Description of R<sub>j</sub>,

j= 0,1,...,p and R<sup>t</sup> is given

at the end of this procedure.

Step 4: If  $\hat{m}_i$  is even, then go to the next step else form  $S=S^*_{-\alpha}^p$  and go to step 6.

Step 5 : Form S =  $S^{\dagger} \cdot \mathfrak{g}_1^p$ .

Step 6: If S = 0 then X is non-negative else it is negative Stop.

Description of the process  $R_0$ :

Start the processes  $R_0$ ,  $R_0^2$ , ...,  $R_0^{i+1}$ ,  $R_0^{i+1}$ , ...,  $R_0^n$

where  $R_0^k$ : Mod  $m_k$  comparator, which compares  $x_k$  and  $x_i^k$ . If compared, then set  $\beta = 1$ , otherwise  $\beta = 0$ , for k=1,2, 0,...,i-1, i+1, ..., n.

If  $x_i \ge 0$ , then set a = 1 else a = 0. Compute a logical variable a as

$$\alpha^{i} = (\beta_{0}^{1} \cdot \beta_{0}^{1} \cdot \beta_{0}^{2} \cdot \beta_{0}^{i-1} \cdot \beta_{0}^{i+1} \cdot \beta_{0}^{n} \cdot a)$$

Description of the process R<sub>j</sub>, j=1,2,

..., p.

Let  $j.m_i \leftrightarrow (/j.m_i^1/m_1,...,/j.m_i^{i-1}/m_{i-1})$

$$/j.m_{i}^{n}/_{m_{n}}),$$

then  $Z^j = x_i + j \cdot m_i \leftrightarrow (z_1^j, z_2^j, \dots, z_{i-1}^j, z_{i+1}^j, \dots, z_n^j)$

where  $z_k^j = /x_i^{k+} /j.m_i^k/m_k, k=1,2,...,n.$

Start the processes  $R_j^1$ ,  $R_j^2$ ,...,  $R_j^{i-1}$ ,

$R_j^{i+1}$ , ...,  $R_j^n$ , where  $R_j^k$ : Mod  $m_k$  comparator which compres  $x_k$  and  $z_k^i$ . If compared, then set  $s_j^k = 1$ , otherwise  $s_j^k = 0$ , for k=1,2, ...,  $s_j^{k-1}$ , ...,  $s_j^{k-1}$

Compute a logical variable a as

Description of the process  $R_{\mathbf{p}}^{\mathbf{i}}$ If  $\mathbf{x}_{\mathbf{i}} \leq 0$ , set  $\mathbf{b} = 1$  else  $\mathbf{b} = 0$ .

Compute a logical variable  $\mathbf{x}$  as

where  $\beta$ , k = 1,2,...,i-1,...,n are p obtained in the same manner as obtained in the case of the process  $R_n$  above.

# Example

Consider the SRNS of 4 pairwise relatively prime moduli 7,5,3,2. Let  $X \iff (1, 1, 1, 0)$  be the number whose sign is to be detected. Choose any modulus, say  $m_1 = 7$  and p = 15.

Step 1 : Start the processes Q1 and Q2

$Q_1$ :  $x_1 = x_1 \longleftrightarrow (1, 1, 1)$  with respect to the moduli 5,3,2

$q_2$ :  $m_1 = m_1 \leftrightarrow (2, 1, 1)$  with respect to the moduli 5,3,2

Step 2: Start the processes  $R_0$ ,  $R_1$ ,...,  $R_{15}$ ,  $R_{15}$

Process  $R_0$ : Start the process  $R_0^2$ ,  $R_0^3$ ,  $R_0^4$ .  $R_0^2$ : Mod  $m_2$  comparator which compares  $x_2$  and  $/x_1/m_2$  i.e.,

compare -1 and -1, in mod 5 comparator. Since they compare, set 2 = 1.

Similarly the processes  $R_0^{3^{\circ}}$  and  $R_0^4$  yield,  $R_0^3 = 1$  and  $R_0^4 = 0$ .

Now  $x_i = x_1 \ge 0$ , set a = 1. Compute a logical variable  $\alpha^0$  as

$$\alpha' = (\beta_0^2, \beta_0^4, \beta_0^4, a) = 1.$$

Process R<sub>1</sub>:

$$z^1 = x_1 + m_1 \leftrightarrow (z_2^1, z_3^1, z_4^1)$$

= (2, -1, 0)

Start the processes  $\hat{R}_1^2$ ,  $\hat{R}_1^3$ ,  $\hat{R}_1^4$ .  $\hat{R}_1^2$ : Compare  $x_2$  and  $z_2^1$  in mod S comparator. They do not compare, so set  $\beta_1^2 = 0$ .

The processes  $R_1^3$  and  $\hat{\pi}_1^4$  give,

$$\beta_1^2 = 0$$

and  $\beta_1^4 = 1$ .

Compute

$$\alpha' = (\beta \cdot \beta \cdot \beta \cdot \beta) = 1$$

Similarly the processes  $R_2$ ,  $R_3$ ,...,  $R_{15}$  are executed simultaneously to yield  $x^2 = x^3 = ... = x^{14} = 1 \text{ and } x^{15} = 0$

Process  $R_{15}$ : Since  $x_1 \ge 0$ , set b = 0.

Compute a logical variable  $x_1 \ge 0$  as

$$\lambda_{1}^{15} = (\beta_{15}^{1} \cdot \beta_{15}^{2} \cdot \beta_{15}^{14} \cdot b) = 1.$$

Step 3: Find 5' =  $(\alpha \circ \alpha \circ \alpha \circ \alpha^{14}) = 1$ . Step 4; Since  $\widehat{m}_1$  is even, form

$$5 = 5' \cdot \alpha = 1.$$

Step 5: Since S = 1, the number X is negative. Stop.

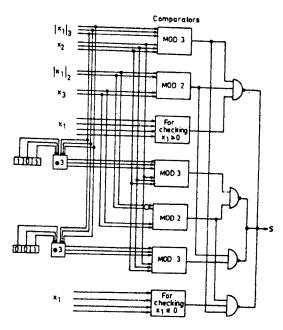

#### HARDWARE REPRESENTATION

A hardware representation of this algorithm, to detect the sign of  $X \longleftrightarrow (x_1, x_2, x_3)$ , is shown in Fig. 1, for the case when the SRNS consists of the moduli 5,3,2. The symmetric residue corresponding to any modulus will be represented in binary representation. It requires one extra bit for sign viz., symmetric residues corresponding to the moduli 5,3,2 are represented in 4,3 and 2 bits respectively.

In Fig. 1 circled '+' denotes the modular addition. The comparators have output 1 only for identical inputs. We use semiconductor gates in our design. The 'e' denotes 'wired OR' function.

Fig. 1 Hardware representation of the scheme for sign detection

Remarks 2: The proposed scheme for sign detection can be generalized to one in which the selected modulus  $m_i$  is replaced by a selected subset of the set  $(m_1, m_2, \dots, m_n)$  of the moduli,  $\hat{m}_i$  is then the product of the remaining moduli.

Remark 3: In the shows implementation, we have considered the case when  $\hat{n}_1$  is even. But if  $\hat{m}_i$  is odd then in the proposed implementation, disconnect the output of the last comparator.

# TIME AND HARDWARE COMPLEXITY REQUIRED FOR THE PROCESS OF SIGN DETECTION

In this section, we estimate the time required to detect the sign of a number in its symmetric residue representation and the hardware complexity.

# Time Required to Compute the Sign

Let T<sub>S</sub>= time required to detect the sign of a residue number,

$$t_{c} = \underset{x_{i} \text{ to } (/x_{i}/_{m_{1}},/x_{i}/_{m_{2}},\cdots,/_{y_{i}}/_{m_{i}-1})}{\text{to } (/x_{i}/_{m_{1}},/x_{i}/_{m_{2}},\cdots,/_{x_{i}}/_{m_{i}-1})},$$

$t_a$ = time required for one residue addition,

\* t = time required by comparator to

compare,

$/x_{i}/_{m_{k}}$  with  $x_{k}$ , k= 1,2,...,i-1, i+1, ..., n,

$t_s$  time required to compute S with the help of  $\alpha^{j_1}s$ .

Then

$T_S \approx t_c + t_a + t^* + \Delta + t_s$ , where  $\Delta$  is a single gate delay.

Assume that combinational logic is used to convert  $x_i$  to  $(/x_i/_{m_1},...,/x_i/_{m_{4-1}},$

$$/\times_{i}/_{m_{i+1}}$$

,...,  $/\times_{i}/_{m_{i}}$ ) is used, then

$T_{\rm S} \approx 8 \Delta + t_{\rm s}$ , where  $t_{\rm a} = 3 \Delta$

### Hardware Complexity

Let  $L_k$ = the number of gates required to convert  $x_i$  to  $/x_i/_{m_k}$ ,

$A_k$ = the number of gates required for mod  $m_k$  adder,

$c_k^{=}$  the number of gates required for mod  $m_k$  comparator,

$D_k$  the number of gates required for comparator, comparing whether  $x_i \ge 0$  or  $x_i \le 0$ , for k = 1, 2, ..., i-1, i+1, ..., n.

For the implementation suggested here, the number of mod  $m_k$  adders used are  $(m_k-1)$ , the number of mod  $m_k$  comparators used are  $m_k$ ,

for  $k=1,2,\ldots,1,1+1,\ldots,n$ . The number of NAND gates used are  $\begin{bmatrix} \hat{m} \\ 1 \end{bmatrix} + 1$ . It is assumed that the NAND gate has fan-in of n. Here, the sign function S is directly obtained by performing 'Wired\_OR' function. But, if

the value of  $\lfloor \frac{m_i}{2} \rfloor$  is very large, then we have to introduce the logical gates. Let T\* be the number of gates required in the last part of our design to get S, then the total complexity estimated (in terms of gates) is

$$\sum_{\substack{k=1\\k\neq i}}^{n} \left\{ L_{k}^{+} A_{k} (m_{k}^{-1}) + C_{k}^{m} m_{k} \right\} + 2 D_{k} + C_{k}^{m} m_{k}^{-1} + C_{k$$

Here we see that the hardware complexity increases with the increase in the range of the system. So, this approach is suitable for MSI/LSI realization. But this scheme saves execution time at the cost of hardware complexity.

#### CONCLUSION

The scheme for sign detection of a number in the SRNS presented in this paper completely does away with the time consuming process of the SMRC. The hardware implementation of the algorithm based on the proposed approach is also suggested. As we have shown that the hardware complexity increases with the increase in the range of the system, it is suitable only for MSI/LSI realization.

### REFERENCES

- Banerji, D.K. and Brzozowski, J.A., Sign Detection in Residue Number Systems, IEEE Trans. on Computers, vol. C-18, pp. 313-320, April 1969.

- Banerji, D.K., Kesidue Arithmetic in Computer Design, Ph.D. Dissertation, Dept of Applied Analysis and Computer Science, University of Waterloo, Ontario, Canada, March 1971.

- Banerji, D.K., On Combinational Logic for Sign Detection in Residue Number Systems, Third IEEE Symposium on Computer Arithmetic, Southern Methodes University, Dallas, Texas, pp. 113-116, November 1975.

- 4 Kaushik, S., On the Arithmetic Operations and Error Correction in Residue Code, Ph.D. Thesis, Indian Institute of Technology, New Delhi, March 1960.

- 5 Szabo, N.S., Sign Detection in Non-Redundant Residue Systems, IRE Trans. on Electronic Computers, vol. EC-11, pp. 494-500, August 1962.

- 6 Szabo, N.S. and Tanaka, R.I., Residue Arithmetic and its Applications to Computer Technology, New Yark! McGraw-Hill, 1967.

### Appendix

# Proof of the theorem

$X \in \begin{bmatrix} -\frac{m}{2} \\ +1, -\frac{m}{2} \end{bmatrix}$  , can be written as

$$X = j m_i + /X/_{m_i}$$

, for some j.

$$\left[-\frac{\hat{m}_1}{2}\right] < j \le \left[\frac{\hat{m}_1}{2}\right],$$

or

$$X = j m_i + x_i$$

, (2)

$$\Rightarrow /X/_{m_k} = /j m_i + x_i/_{m_k}$$

for  $k = 1, 2, ..., i-1, i+1, ..., n$ ,

or  $x_k = /j m_i + x_i/_{m_k}$ .

It is obvious that X is non-negative in the range  $[0, \lfloor \frac{m}{2} \rfloor]$ . There are two cases.

Case (a): If

$$\hat{m}_i$$

is odd, then for non-negative  $X_i$  j is bounded between 1 and  $\begin{bmatrix} \hat{m}_i \\ 2 \end{bmatrix}$ , since for  $j=1$

$$0 < X = m_i + x_i < \begin{bmatrix} \frac{M}{2} \end{bmatrix}$$

and for  $j = \begin{bmatrix} \hat{m}_i \\ 2 \end{bmatrix}$

$$0 < X = \begin{bmatrix} \hat{m}_i \\ 2 \end{bmatrix}$$

$$0 < X = \begin{bmatrix} \hat{m}_i \\ 2 \end{bmatrix}$$

If j = 0 then equation (2) becomes  $X = x_i$ ,

For non-negative X,

$$X \ge 0 = x_i \ge 0.$$

In conclusion, we say that  $\boldsymbol{X}$  is non-negative iff

Case (b): If

$$\hat{m}_i$$

is even, then  $\hat{m}_i = \frac{\hat{m}_i}{2} = \frac{\hat{m}_i}{2}$

For

$$j = \lfloor \frac{\hat{m}_{i}}{2} \rfloor$$

, we get

$$X = \lfloor \frac{\hat{m}_{i}}{2} \rfloor, m_{i} + x_{i}, \text{ by using (2),}$$

$X = \frac{\hat{m}_{1} \cdot m_{i}}{2} + x_{i} = \frac{m}{2} + x_{i} = \lfloor \frac{m}{2} \rfloor + x_{i}$

since M is even. For non-negative X,  $X \leq \lfloor \frac{M}{2} \rfloor$ ,

therefore from above equation  $x_i \le 0$ . For j = 0,  $x_i \ge 0$  (shown in case (a)). Hence X is non-negative iff

$$\begin{bmatrix}

\frac{\hat{m}_{i}}{2} - 1 \\

V & \{ x_{k} = /j \cdot m_{i} + x_{i} / m_{k} \} \\

j=1 & V \{ x_{k} = / \lfloor \frac{\hat{m}_{i}}{2} \rfloor m_{i} + x_{i} / m_{k} \wedge x_{i} \leq 0 \}$$

$$V \{ x_{k} = / x_{i} / m_{k} \wedge x_{i} \geq 0 \} \text{ is true.}$$