## A SYSTEMATIC APPROACH TO THE DESIGN OF STRUCTURES FOR ADDITION AND SUBTRACTION \_ CASE OF RADIX $r = m^k$ -

Diem Dinh Nguyen

University of Illinois at Urbana-Champaign Urbana, IL, 61801

ABSTRACT

The results of Robertson concerning a systematic approach to the design of Adder/Subtracter structures of radix r= 2 k, k I are generalised to cover all structures of radix r= mk, k I and m > 2 The use of Guasibinary representations help reduce the number of types of fundamental structures required. In addition to the types encountered in the earlier case, only one new type of fundamental structures called Radix-m Carry Generator is needed. Examples in the particular case of Decimal Adder/Subtracter structures are used to illustrate the

I.Introduction

results.

A design theory for a class structures for Addition and Subtraction is presented in a recent paper . An Adder/ Subtracter structure is one that trans forms one or more input operands into one or more output operands where each input and output operand is a digit set, i.e. a consecutive sequence of integers including zero and the transformation is subjected to some precise rules . In essence, the above paper demonstrates that a complex Adder/Subtracter structure can be realised as combinations of simpler fundamental structures with known or more easily determined implentations . The input and output operands of each type of fundamental structures are either two-valued or three-valued digit sets .

A distinguishing feature for this design theory is the partition of given digit sets with more than three values into binary weighted two-valued and three-valued digit sets. Such a partition is referred to in this paper as a Quasibinary representation, in contrast to the conventional Finary representations which consist only of binary weighted two-valued digit sets. Eccause a three-valued digit set can be replaced by two two-valued digit sets, Quasibinary representations as special cases. Furthermore, because the

three-valued digit set is a redundant digit set with respect to the basic radix r=2 of the fundamental structures mentioned above, the use of Quasibinary representations incorporates in a natural way this type of redundancy which is known to lead to improvements in the design of arithmetic structures 2-8.

The design process consists of two steps. The first step involves the decomposition of the given structure into fundamental structures and the second step the filling in of implementation details of the fundamental structures being used. There also exist relations that provide partial measures of the hardware costs and some guidelines in the decomposition step of the design process.

The main restriction on the results of I is that the Adder/Subtracter structures to be designed must have radix r of the form  $r=2^k$ ,  $k\geqslant I$ . Since some Adder/Subtracter structures of intrest do not fall into the above class ( one eminent case being the class of Decimal Adder/Subtracter structures ), this paper generalises those results to deal with Adder/Subtracter structures of radix  $r=m^k$ ,  $k\geqslant I$  and  $m\geqslant 2$ .

As will be seen , the Quasibinaryrepresentation will again assume an important role. Its use leads to a considerable reduction in the number of types of fundamental structures required in the decomposition step . The set of fundamental structures for the case of radix r=  $m^k$ ,  $k \geqslant I$ , m > 2 contains those same fundamental structures for the case of radix ,  $k \geqslant \mbox{\tt I}$  , plus a new type called Radix-m Carry Generator . There exist other differences between the two cases; some of these differences appear in examples concerning designs of Decimal Adder/ Subtracter structures of radix r = IO\* k > I . This class of structures is considered not only to illustrate the theory but also because of its possible application value .

Due to space limitations , the proofs of all results together with many clarifying illustrations will be omitted . The

reader is referred to 9 for details . The paper is organised as follows. Section 2 reviews the basic concepts and notations Section 3 contains the main results , Section 4 presents some illustrative examples and Section 5 provides some concluding remarks .

2. Digit sets and Adder/ A (6+I)-valued digit set is a sequence of 6+I consecutive integers including zero {-w,-w+I,...,-w+6} where O < w < 6. 6 is called the <u>diminished cardinality</u> and w the <u>offset</u> of the digit set. Let r be the radix involved, a digit set is redundant if  $\delta > r-I$  , nonredundant if  $\delta = r-I$  . Since r can be as low as 2 , the lower limit of § is I. There is no upper limit for § but we use the arbitrary upper limit 2(r-I) which is sufficiently large for most practical

purposes . The digit set is said to be normalised if w=0 , symmetric if  $\delta$  is even and  $w = \frac{\delta}{2}$ .

Digit sets will be denoted by letters of the alphabet with a superscript indicating the offset. For example  $a = \{0,1\}$ ,  $a^{I} = \{\overline{1},0\}$ ,  $b^{O} = \{0,1,2\}$ ,  $b^{I} = \{\overline{1},0,1\}$ ,  $b^{2} = \{\overline{2},\overline{1},0\}$ , ...,  $i = \{0,1,2,4\}$ ,  $b^{I} = \{\overline{1},0,1\}$ ,  $b^{I} = \{\overline{2},\overline{1},0\}$ ... It is important that the three-valued digit set  $\textbf{b}^{\text{W}}$  ( also any digit set with larger number of values ) be recognised as a separate entity, independent of its binary representation. It is also useful to refer to the class of digit sets of a given diminished cardinality without specifying the offset by omitting the superscript in the digit set symbol .

A set of integers A is a Setsum of the sets of integers  $\ensuremath{\mathbb{B}}$  and  $\ensuremath{\text{C}}$  if and only if for every b € E and c € C there exists an a & A such that a=b+c. Using the symbol '+' for Set Addition operation , we can write either A = B + C or A = C + B due to

its commutative property .

A Quasibinary representation of a given digit set is a partition into binary weighted two-valued digit sets (a) and three-valued digit sets (b) such that the Setsum of these binary weighted components equals the original digit set . A simple algorithm to find such representations is given in 1:

> Algoritm: Given a digit set & w with \$>2 O) (Ignore the offset w till Step 2) INITIALISE 140; 6, 46.

>

> I) WHILE 6, > 0 DO

EEGIN IF & is ODD , THEN include 2<sup>i</sup>a as a component;  $\mathbf{\xi}_{i+1} = \frac{1}{2} (\mathbf{\xi}_{i} - I)$ . ELSE include  $2^{i}b$  as a

component,  $\delta_{i+1} = \frac{1}{2}(\delta_i - 2)$ .  $i \leftarrow i + I$ .

2) IF w=O , THEN assign offset O to all components; ELSE (w>O) assign offsets to individual components in the representation found above so that their weighted sum is equal to w ( Note: There may be more than one way to do this ). 3) END.

For example , without taking offset into account , the digit set n (with (= 14) has the Quasibinary representation 4b \$25 \$b .Thus the normalised digit set no has the unique Quasibinary representation 4b0.  $2b^{0} + b^{0}$ . In contrast, the digit set  $n^{4}$  can have either  $4b^{I} + 2b^{0} + b^{0}$  or  $4b^{0} + 2b^{I} + b^{I}$  as a Quasibinary representation .

A representation is said to overrepresent a digit set if it can represent values other than those belonging to the digit set in question . A close examination of the definition and formation of Quasibinary representations show that the problem of overrepresentation will never occur . In comparison , such a problem may occur when one uses Two's Complement binary representations (and other well-known Einary representations). For example the symmetric digit set {8,7,...,0,...,7,8} has a Quasibinary representation 8a4 4a4 2a4 b, but for Two's Complement binary representation, one is forced to use I6a + 8a + 4a + 2a + a which can represent also the values (I6, I5, ..., 9) and (9, I0, ..., I5) not in the desired digit set. If the digit set is an input operand, overrepresentation does not cause any problem in logical design . In fact , it helps simplify the result because the so-called overrepresentations are simply DON'TCARES . If however the digit set is an output operand, overrepresentation leads to additional constraint to the logical design problem so that the combinations corresponding to the DON'TCARES will never appear at the the output . In practice , sometimes over-representation of a digit set may be used deliberately to gain some saving in bit storage; the effort in modifying the design and/or the extra hardware cost to achieve this may be justified in those

cases .

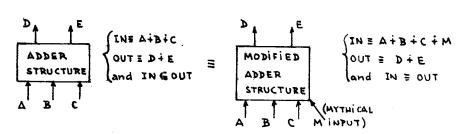

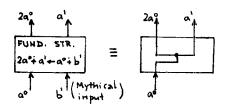

Because an Adder becomes a Subtracter by a change of sign or by changing the value of a single input and because some structures in the following discussion possess a mixture of properties of Adder and Subtracter and are difficult to characterise , we shall use the terminology of Addition to refer collectively to all structures. An Adder structure transforms one or more digit sets (inputs) into one or more digit sets (outputs) such that the Setsum of the outputs contains that of the inputs. To help make the decomposition step in the design process more uniform, we adopt the convention that if the above Set Containment is proper a Mythical Input digit set, to the extent necessary to make the Input Setsum equal to the Output Setsum will be introduced as shown in Fig. I. Because the Mythical Inputs are just dummy inputs, they can be used to simplify the structure in the final stage of the design process. The introduction of Mythical Inputs therefore does not increase complexity of the final design. Fig. 2 presents a typical example.

Each Adder structure has a negative found by replacing each of the input and output digit sets by its negative. If all input and output digit sets are nonredundant, the logical designs of a structure and its negative are identical. For a structure with redundant digit sets, difficulties are apparently encountered with symmetric digit sets but these can be easi-

ly resolved .

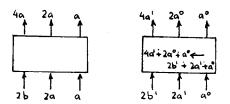

In the following, an Adder structure will be denoted by a symbol consisting of the Setsum of the inputs on the right side and that of the outputs on the left side of the transformation sign '-'. For example, the class of Adder structures of Fig. 3.a is designated by 4a+2a+a-2b+2a+a while one of its variant, shown in Fig. 3.b, is designated by 4a<sup>I</sup>+2a<sup>O</sup>+a<sup>O</sup>-2b<sup>I</sup>+2a<sup>I</sup>+a<sup>O</sup>.

3.General results

The first four results of this section show different types of fundamental structures required in the decomposition of Adder structures of radix r=m ,k> I and m>2. The last result gives a set of relations between the numbers of different types of fundamental structures involved in the decompositions and various parameters associated with the original Adder structure.

Result I: Any Adder structure of radix r=mk, k > I, m > 2 can be decomposed into at least one combination of the following types of fundamental structures.

Note that the digit sets involved have diminished cardinalities ranging from I up to (2m-I). The presence of allowed digit sets with \$\frac{6}{2}\$ creates some practical problems. It has been shown that a digit set b (\$\frac{6}{2}\$2) when implemented by two binary variables (two bits) has 9 different formats; each one represents an NP equivalent group and may lead to a different logical design and hence need be considered individually. A digit set with \$\frac{6}{2}\$ (such that \$\frac{6}{2}\$)

$\neq$  2<sup>k</sup>-I ) will have many more formats . For example, a digit set d  $(\delta=4)$  when implemented with 3 bits has 30236 formats while a digit set e (6=5) has 20580 formats. The task of carrrying out logical designs for all possible versions of a type of fundamental structure corresponding to all formats of allowed digit sets soon becomes enormous and impractical . This in turn makes the selection of one among those formats to be used more difficult. To allewiate this problem, it is decided to replace all allowed digit sets of the given Adder structure by their Quasibinary representations. We then only have to deal with the digit set a with a single format and the digit set b with 9 different formats as mentioned above .As a consequence of the decision to use Quasibinary representations, we also obtain a reduction in the number of different types of fundamental structures .

Result 2: Under the decision to use Quasibinary representations, the set of fundamental structures of Result I becomes

ma

$$\dotplus$$

$Q_{(m-1)}$   $\longleftarrow$   $Q_{(2m-1)}$

2a  $\dotplus$  a  $\longleftarrow$  b  $\dotplus$  a

a  $\dotplus$  a  $\longleftarrow$  b

b  $\dotplus$  a  $\longleftarrow$  a  $\dotplus$  a

b  $\dotplus$  a  $\longleftarrow$  2a  $\dotplus$  a

$Q_{(2m-1)}$   $\longleftarrow$  ma  $\dotplus$   $Q_{(m-1)}$

where  $Q_{\rm t}$  the Quasibinary representation of the digit set with the diminished cardinality  $\delta$ :

A further reduction follows if we use the so-called FanOut Operators, which in this paper take the general form  $n_{I}a + n_{2}a \leftarrow n_{3}a$  with  $n_{I}, n_{2}, n_{3} > 0$  and  $n_{I} + n_{2} = n_{3}a$

n<sub>3</sub>

Result 3: An equivalent set of fundamental structures to that of Result 2 is

is

ma

$$\neq Q_{(m-1)}$$

$\leftarrow Q_{(2m-1)}$

2a  $\neq a$   $\leftarrow b$   $\neq a$

a  $\neq a$   $\leftarrow b$

n<sub>1</sub>  $\neq n_2$   $\leftarrow n_3$  with  $n_1, n_2, n_3$

O and  $n_1 + n_2 \cdot n_3$

Thus , in addition to the fundamental structures of the four types ( Radix-2 Carry Generator , Generalised Half-Adder, Converter and FanOut Operator ) which are encountered in the decomposition of Adder structures of radix  $r=2^k$  ,  $k\geqslant I$  we need only a new type , ma  $\neq Q$  (m-I) General m>2 . As an illustration , for the class of Decimal Adder structures ( m=IO ) , the set of fundamental structures is

If in particular m is not a prime integer but of the form m =  $2^{9}$ .p where q > 1 and p is a prime integer , we also have

Result 4: If m = 2<sup>9</sup>, p with q > I and p a prime integer, the set of fundamental structures for Adder structures of radix r = m<sup>k</sup>, k > I, m > 2 is the same as that for Adder structures of radix r = p<sup>k</sup>, k I with p as defined.

For the illustrative case of Decimal Adder structures (  $m = 10 = 2^{4}.5$  ), Result 4 means that ,in the set of fundamental structures , the Radix-IO Carry Generator IOa+4a+2b+a  $\leftarrow$  8a+4b+2a+a is replaced by the Radix-5 Carry Generator  $5a+2a+b \leftarrow 4a+2b+a$ .

Let dim (want) and \$\beta\_{im}(\beta\_{ont})\$ denote the number of a digit sets and bdigit sets respectively on the input side (output side) of an Adder structure. Let \$\lambda\_{im}(\beta\_{ont})\$ denote the "information content" of the input (the output) of the same Adder structure. Following, each a digit set is assumed to have one unit of information while each b digit set two units for convenience. Let \$\Delta\_{ont} = \Delta\_{ont} = \

and b digit sets respectively which have weights that are multiples of m on the output side of an Adder structure of radix r=m<sup>k</sup>, k > I , m > 2 and define 5m = 5m + 25m. Finally let z<sub>m</sub>, z , y , x and u denote the number of each Radix-m Carry Generators, Radix-2 Carry generator, Generalised Half-Adders, Converters and FanOut Operators respectively being used in a decomposition . We have:

Result 5: The following relations hold for any decomposition of an Adder structure of radix r=m k,k > I, m > 2 using the fundamental structures of Result 3

$$z_{m} \geqslant \delta_{m}$$

$z + \lambda_{m} z_{m} - u = \Delta \lambda$

$y - x + (\alpha_{m} + \beta_{m}) z_{m} - u = \Delta \lambda - \Delta \beta$

If the only goal is to minimise hardware cost by reducing the numbers of each type of fundamental structures used in a decomposition, the above relations indicate that one should try to use as few Converters and FanOut Operators as possible. Each increase in u leads to an increase in either z or  $z_m$  or y while each increase in x causes an increase in y . In practice , another goal in the final design is the total Time Delay due to logic gates, which is usually in conflict with the above goal and forces the designer to select a compromise . Now for a given Adder structure, the parameters  $\Delta \beta$ ,  $\Delta \lambda$  and are fixed (note that by definition  $\Delta \alpha = \Delta \lambda - 2\Delta \beta$ ) and the above relations can serve another function as a rough measure of hardware cost or help establish lower and upper bounds on this cost as has been done in 1

For the particular case of Decimal Adder structures ( $m = 10 = 2^{\circ}.5$ ), the above relations take the forms  $z_5 > \sigma_{10}$ ,  $z - u = \Delta\lambda$ , and  $y - x - u = \Delta\lambda - \Delta\beta$  since the Radix-5 Carry Generator is being used and  $\alpha_5 = \beta_5 = \lambda_5 = 0$ .

4. Examples of some Decimal Adder structures Designs

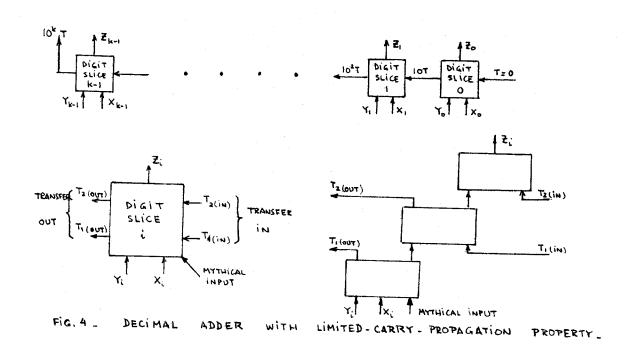

We consider designs of Decimal Digit Slices of Decimal Adders with the Limited -Carry-Propagation property. Each slice is constrained to have the form shown in Fig. 4, where X,Y,Z and the Mythical Input are the operands and T<sub>I</sub>(in), T<sub>2</sub>(in), T<sub>1</sub>(out), and T<sub>2</sub>(out) are two-valued Transfer In and Transfer Out signals respectively.

The decomposition step can be summerised using an Information Loss Chart which provides traces of important parameters in the decomposition . These parameters are the quantities  $\alpha$ ,  $\beta$ ,  $\lambda$ , the number of a digit sets and b digit sets of the same weights (together with their

offsets ) that are available at each stage and the numbers of each type of fundamental structures to be used in that stage. For examples, the symbol 2 in the column 8a implies that there exist one 8a and one 8a digit sets, the symbol I in the column 4b implies that there exist one 4b digit set at that stage and the symbol 2@[2a +a ←b +a] means that two Radix-2 Carry Generators are used . In cases of ambiguities , more explicit symbols will be needed . For example , the symbol 22 in column 8b may mean either two 8b1 digit sets or one 8b° plus one 8b² digit sets. To avoid such ambiguities, we shall use I', I' for the former and I o, I2 for the latter case. The first row of each Information Loss Chart , beneath the column headings, contain walues of the above quantities which are present on the input sideof an Adder structure to be designed . In the following rows , the values of parameters will vary ( i.e. may increase, decrease or remain unchanged depending on the particular fundamental structures being used in the row immediately above ) . This continues until a pattern of weighted a and b digit sets exactly the same as that of the desired output is obtained. The Information Loss Chart so derived contains enough information that can be quickly translated into a block diagram layout .

Note that in the examples given below we only present for illustrative purposes what appear to be "reasonable" designs and do not claim that they are optimal ones.

Example I: Common digit set for the input and output operands is  $n'=\{7,6,\ldots,0,\ldots,6,7_2\}$ . A Mythical Input digit set ,namely  $d^2=\{2,\overline{1},0,I,2\}$ , is necessary in this case. After replacing each digit set by its Quasibinary representation, we obtain one as shown in the Information Loss Chart of Table I.

Note the 'J' marks in the Information Loss Chart which emphasise the fact that each Transfer In signal can only be used after its Transfer Out counterpart has been generated as indicated earlier in Fig. 4.

Example 2: Common digit set for the input and output operands is o \$=\{\overline{8},\overline{7},\dots\overline{0}}\). Again a Mythical Input digit set ,namely c \$\{\overline{1},0,I,2\}\], is necessary. After replacing each digit set by its Quasibinary representation , we obtain one decomposition as shown in the Information Loss Chart of Table II.

Note that ,in common electronic implementation of the fundamental structures, the FanOut Operators require no hardware and hence no Time Delay, its presence can be assimilated into the other fundamental structures, as illustrated in Fig.5 which

occurs in the first stage of this example.

Beyond confirming the relations of Result 5, the examples above (and others not presented here )lead to the following observations. As expected, due to the presence of an additional type of fundamental structures , the Radix-m Carry Generator the decomposition process becomes more complicated. In the case of radix  $r = 2^k$ , a reasonable decomposition strategy that seems to have always working. seems to have always worked is to combine the a and b digit sets of the same weights as quickly as they become available to generate higher weighted digit sets while at the same time avoiding the use of Converters as much as possible. This is because the available a and b digit sets are always in proper form for combinations using either Radix-2 Carry Generators or Generalised Half-Adders ( except when all inputs are b digit sets where one is forced to use the Converters to keep the decomposition going ) and because there are no ouput signals with weights other than  $2^k$ ,  $k \geqslant I_k$ . In contrast , in the case of radix  $r = m^k$  k > 1 with m > 2 , the attention must focus on generating output signals with weights of the form mk via Radix-m Carry Generators. Usually, one needs to rearrange the available digit sets before they are in proper form ready to be used as inputs to the Radix-m Carry Generators in order to generate the desired outputs . These rearrangements often require the use of FanOut Operators , of Converters and extra Time Delays . This means that it is not possible to state a general strategy for the case of radix r = m, k>I , m > 2. This also explains the fact that while the use of FanOut Operators may be avoided entirely (except for pathological cases of little practical interest ) in the case of radix r=2k,k>I, such is not the case for radix r=mk, k> I, m>2, with Example 2 as an illustration

To complete the designs of the examples one has to fill in the implementation details of the fundamental structures . The logical designs of all versions of all variants of the last four types of fundamental structures for radix r=10k, k > I, are given in 1. It remains to consider the logical designs of the Radix-5 Carry Generators. There exist I4 variants of this type of fundamental structures, each one corresponds to a value of the offset. Because each such structure involves 2 b digit sets, each one can independently assume one of the 9 formats mentioned earlier, 8I versions of logical designs for each variant must be considered . Because the logical designs structures which are negative of one another are identical or can be easily deduced from one another ,we need only concern with 7 different variants and hence (7 \* 8I) = 567 different logical design problems, each one with 4 binary va-

riables as inputs and 4 variables as outputs . Again space limitations prevent discussions of these logical designs here.Reference 9 contains two typical designs as examples. When the need arises the designer can carry out similar designs which are not difficult in nature .

Based on our limited designs experiences, we cannot ascertain which format for the b digit sets in the Radix-m Carry Generators would results in better designs. However, for practical cases that we have come across the number of Radix-m Carry Generators required is uasually small in comparison to the numbers of Radix-2 Carry Generators, and Generalised Half-Adders. As a consequence , the observation  $^{\rm I}$  that the use of Format #2 or Format #3 would result in overall better designs in terms of gate counts could be expected to hold true for the case of radix  $r=m^k$ , k > I, m >2 as in the case of radix  $r=2^k$ , k > I.

## 5.Conclusion

The results of Robertson 1 concerning a systematic approach to the design of Adder/Subtracter structures of radix r = 2k k > I have been generalised to cover all structures of radix r=mk, k>I, m>2. The use of the so-called Quasibinary representations for all digit sets involved in these structures is shown to play an important role here as in the earlier case . In addition to the four types of fundamental structures already discussed in , only one new type , called the Radix-m Carry Genera-

is needed. There exist other small differences between the case of radix r=2k, k>I and the case of radix r=mk, k>I, m>2. Some examples involving Decimal Adder structures illustrate these differences. The observations made for these examples hold true for other values of m > 2 as well . As in the case of radix r = 2 k, k > I, it is possible to derive a set of relations connecting the numbers of different types of fundamental structures being used in any design and the parameters of that design problem, which may be of use to the designer .

As can be seen several issues concerning the application of the approach to practical problems are left untouched .Issues such as the choice of a particular representation for the Mythical Input the compromise between hardware complexity and speed ... must be dealt with by the designer of these problems .

## ACKNOWLEDGEMENTS

To Professor James E. Robertson for his support and guidance and to the National Science Foundation for its financial support ( NSF Grant MCS 80-00058 )

## BIBLIOGRAPHY

I. ROBERTSON J.E. " A Systematic Approach to the Design of Structures for Arithmetic" Tech. Rept. UIUCDCS-R-80-IO04 ,Dept. of Computer Science , University of Illinois

at Urbana-Champaign, Jan. 1981 .

2. ATKINS D.E. "Introduction to the role of Redundancy in Computer Arithmetic ",

Computer , Jun. 1975 .

3. ATKINS D.E. "Design of the Arithmetic Unit of ILLIAC III: Use of Redundancy and Higher Radix Method ",IEEE Trans. on Computers, vol. C-19, N. 8, Aug. 1970.

4. BOROVEC R.T. "The Logical Design of

- a Class of Limited-Carry-Propagation Adders Tech. Rept. 275, Dept. of Computer Science, University of Illinois at Urbana-Champaign, 1968

- 5. CHOW C.Y. and ROBERTSON J.E. "Logical Design of a Redundant Binary Adder " Proc. of Second Symp. on Computer Arithmetic, I978

- 6. METZE G.A. and ROBERTSON J.E. " Elimination of Carry Propagation in Digital Computres " Proc. of Int. Conf. on Information

- Processing, Paris, France, Jun. 1959.

7. ROBERTSON J.E. Lecture Notes for CS

364, Dept. of Computer Science, Universty

of Illinois at Urbana-Champaign, Aug. 1979.

8. ROHATSCH F.A. "A Study of Transformation Applicable to the Development of Limited-Carry-Borrow-Propagation Adders" Tech.

Rent. 226 Dept. of Computer Science University Rept. 226, Dept. of Computer Science, University of Illinois at Urbana-Champaign, Jun.1967

- 9. NGUYEN D.D. "A Systematic Approach to the Design of Structures for Addition and Subtraction \_ Case of Radix r = m ." Tech. Rept. UIUCDCS-R-80-I049 , Dept. of Computer Science , University of Illinois at Urbana Champaign , Dec. 1980 .

FIG. 1\_ USE OF MYTHICAL INPUT DIGIT SET

FIG. 2. FUNDAMENTAL STRUCTURE

WITH A MYTHICAL INPUT AND

CORRESPONDING REDUCED STRUCTURE.

FIG. 3.A FIG. 3.B

EXAMPLE OF A FUNDAMENTAL

STRUCTURE AND ONE OF ITS VARIANT.

TABLE I

|    |   |   | 10 |    | 8 |    | 4     |    | 2  |    | 1  |     | Numbers and types of                   |

|----|---|---|----|----|---|----|-------|----|----|----|----|-----|----------------------------------------|

| y  | ß | α | Ь  | a  | Ь | a  | Ь     | а  | Ь  | a  | Ь  | a   | fundamental structures                 |

| 14 | 6 | 2 |    |    |   |    | じじ    | -  | じじ | 2' | じじ |     | {1@[a+a←b]<br>{2@[2a+a←b+a]            |

|    |   |   |    |    |   |    | 1',1' | 2' |    | 2° | ۱, | 21  | { 1@[b ← a + a]<br>[3@[2a + a ← b + a] |

|    |   |   |    |    |   | 22 |       | 2° | ۱° | 1, |    | 2°  | [2@[b←a+a]<br>[1@[2a+a←b+a]            |

|    |   |   |    |    |   | 22 | 10    | 1° |    | 1' | 10 |     | {  @[sa + 2a + b - 4a + 2b+a           |

| 8  | 2 | 4 |    | 11 |   | 1, |       | 2° | l° |    | l° |     |                                        |

| 8  | 2 | 4 |    |    |   | 11 |       | 2° | 10 |    | 10 | 1'  | d {1@[b←a+a]<br>1@[2a+a←b+a]           |

|    |   |   |    |    |   | 11 | l°    |    | 10 | 10 |    | 1.  | [1@[2a+a ←b+a]                         |

|    |   |   |    |    |   | l¹ | l.    | 10 |    | 10 |    | 11  | { 1@ [5a+ 2a+b+ 4a+2b+a]               |

| 6  | ١ | 4 |    | 10 |   |    |       | 2, | ۱' |    |    | 1,, |                                        |

| 6  | I | 4 | -  |    |   |    |       | 2' | i' |    |    | 2'  | →{2@[b+a+a]                            |

|    |   |   |    |    |   |    | 11    |    | 11 |    | 1, |     |                                        |

SUMMARY:  $\Delta \lambda = 8$ ,  $\Delta \beta = 3$ ,  $\Delta \alpha = 2$  and  $\delta_{10} = 2$ .  $Z_5 = 2$ , Z=8, y=4, x=1 and u=0. Time DELAY= 8 UNITS.

TABLE I

|    |     |     | $ \top $ | 10 |    | 8 |    | 4    |    | 2  |    | т  | [  | I Mark and the second                           |

|----|-----|-----|----------|----|----|---|----|------|----|----|----|----|----|-------------------------------------------------|

| λ  | A B | 3 0 | × [      | Ь  | a  | Ь | а  | Ь    | a  | Ь  | a  | Ь  | a  | Numbers and types of fundamental structures     |

| 10 |     | 0 1 | ٥        |    |    |   | 22 |      | 2° |    | 3° |    | 31 | {1@ FANOUT; 4@[b+a+a]                           |

|    |     |     |          |    |    |   | 1' | 1,1' |    | 1. | 10 | 10 | 11 | \$1@ [2a+a + b+a]<br>{1@[5a+2a+b+4a+2b+a]       |

| 10 |     | 5 4 | 4        |    | 1, |   |    | 1,   | 10 | 21 | 10 |    | 1, |                                                 |

| 10 | 3   | 5 4 | -        |    |    |   |    | ۱'   | 10 | 21 | 10 |    | 22 | {  @[b+a+a]<br> 2@[2a+a+b+a]                    |

|    |     |     |          |    |    |   | 10 |      | 21 | lo | 11 | 12 |    | {   @ [ b + a + a ]<br>    @ [ 2a + a + b + a ] |

|    |     |     | -        |    |    |   | 1° | 1,   | l° |    | l' | 12 |    | {1@[5a+2a+b+4a+2b+a]                            |

| 7  | 2   | 3   | 1        |    | 10 |   |    |      | 2١ | ι' |    | 12 |    | -                                               |

| 7  | 2   | 3   |          |    |    |   |    |      | 21 | Į1 |    | 12 | l* | 1 {1@[b + a + a]<br>1@[2a + a + b + a]          |

|    |     |     | L        |    |    |   |    | 1,   |    | 1, | 11 |    | 1° | {1@[2a+a + b+a]                                 |

|    |     |     | L        |    |    |   |    | 1,   | 1, |    | 1° |    | 10 | {1@[2a+a + b+a]                                 |

|    |     |     |          |    |    |   | 11 |      | ٥١ |    | 1° |    | 1. |                                                 |

SUMMARY:  $\Delta\lambda$  = 6,  $\Delta\beta$  = 0,  $\Delta\alpha$  = 6,  $\sigma_{10}$  = 2.  $z_{5}$  = 2,  $z_{7}$  7,  $y_{7}$  7,  $z_{7}$  0,  $u_{7}$  1. TIME DELAY = 8 UNITS.