### A MULTIOPERAND TWO'S COMPLEMENT ADDITION ALGORITHM

#### Hideaki Kobayashi

Department of Electrical and Computer Engineering University of South Carolina Columbia, SC 29208

#### ABSTRACT

This paper presents a novel algorithm for summing a set of 2's complement numbers in parallel. The 2's complement addition is converted to an equivalent parallel summation of unsigned numbers. The conversion is performed by simply complementing all the sign bits. Only a few constant bits are required for sign correction. This algorithm is suitable for computer-aided design (CAD) of custom VLSI.

#### INTRODUCTION

Multioperand addition is essential in parallel convolution necessary for real-time signal and image processing [1]. Baugh and Wooley's algorithm [2] allows unsigned implementation techniqes for parallel multiplication. However, a set of signed product terms generated by these multipliers needs to be summed in parallel.

This paper describes a parallel algorithm for adding a set of 2's complement numbers. Carry-save adder (CSA) networks synthesized by a CAD tool [3] are used as implementation examples.

#### ALGORITHM

The sum S of M  $% \left( 1\right) =1$  numbers is expressed as:

$$S = \begin{array}{c} M \\ SUM \\ k=1 \end{array} \begin{bmatrix} -x(n-1)k & 2 & -1 & n-2 & i \\ 2 & + & SUM \\ i=0 & i=0 \end{bmatrix}$$

where x(n-1)k is the sign bit and xik is the i-th significant bit of the k-th operand. The negative term in (1) is replaced by

where  $\overline{x}(n-1)k$  is the complement of the sign bit. Eq. (1) is then rewritten as:

$$S = \underset{k=1}{\text{SUM}} \overline{x}(n-k)k 2 + \underset{k=1}{\text{SUM}} \underset{i=0}{\text{SUM}} xik 2$$

$$n-1$$

(2)

where the negative term depends on only the number M of operands.

The following two cases of M-operand addition are considered. CSA networks are used as implementation examples.

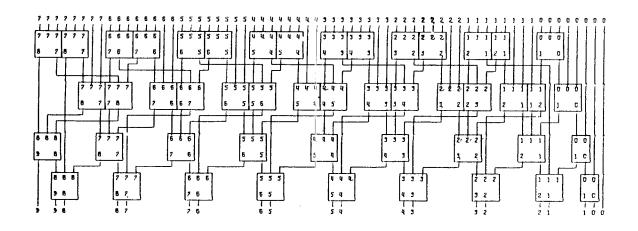

Case A: M is the d-th power of 2, where d is an integer. The negative term in (2) is only the (n-1+d)th power of 2. Figure 1 shows a CSA network [3] for M = 8 and n = 8, where "o's" are positive bits and "o's" are complemented sign bits. Note that all summand bits are positive allowing unsigned implementation techniques for parallel addition. The sum is obtained by simply complementing the most significant bit (MSB).

Case B: M is not the d-th power of 2. The negative term in (2) is:

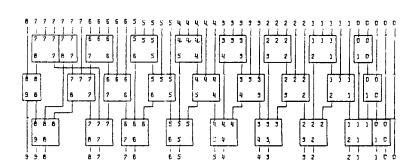

Figure 2 shows a CSA network for M = 5 and n = 8, where "l's" are constant bits for sign correction. The sum is obtained by simply complementing the MSB.

# CONCLUSION

A new algorithm for parallel two's complement addition has been presented. The complexity of parallel 2's complement adders is significantly reduced by simply complementing all the sign bits. This approach is applicable for CAD of custom VLSI.

## REFERENCES

- 1. H. Kobayashi and Y. P. Foo,

"Programmable Logic for Parallel

Convolution," IEEE Int. Conf.

Computer Design: VLSI in Computers,

Port Chester, NY, Oct. 1984, pp.

700-704.

- C. R. Baugh and B. A. Wooley, "A Two's Complement Parallel Array Multiplication Algorithm," IEEE Trans. Comput., vol. C-22, pp. 1045-1047, Dec. 1973.

- H. Kobayashi and T. A. Snith, "SPAN: A Synthesis Program for Adder Networks," 1st Int. Conf. Computers and Applications, Beijing, China, June 1984, pp. 710-714.

SPAN V1.00

|                    |                                                       | 5-OCT-1984 |       |     |        |           | 13:39:53.93 |                          |       |       |        |

|--------------------|-------------------------------------------------------|------------|-------|-----|--------|-----------|-------------|--------------------------|-------|-------|--------|

| 1222242            | ****                                                  | ***        |       |     | * = =  | all Mr 26 |             |                          |       | ****  | ****** |

|                    |                                                       | •          | 0     | 0   | 0      | 0         | 0           | 0                        | <br>0 |       |        |

|                    |                                                       | •          | 0     | 0   | 0      | 0         | 0           | 0                        | 0     |       |        |

|                    |                                                       | :          | 0 0 0 | 0   | 0 0 0  | 0         | 0 0         | 0 0 0                    | 0 0   |       |        |

|                    |                                                       | ·          |       |     | °      | <u>-</u>  | <br>0       | 0<br>                    |       | 14-FA | 1-на   |

|                    | ō                                                     | 0          | 0 0 0 | 0 0 | 0 0 0  | 0         | 0 0         | 0 0 0                    | 0 0   |       |        |

|                    |                                                       | 0          | 0     | 0   | 0      | 0         | 0           | 0                        | 0     |       |        |

|                    | 0                                                     | 0          | 0     | 0   | 0      | 0         | <br>0       | 0                        | 0     | 14-FA | 1-на   |

|                    | 0                                                     | 0          | 0     | 0   | 0      | 0         | 0           | 0                        | 0     | 8-FA  | 1-HA   |

| (                  | 0                                                     | 0          | 0     | 0   | 0 0    | 0         | 0           | 0                        | 0     |       |        |

|                    | 0<br>                                                 | <u>-</u> - | 0<br> |     | °<br>• | <u>.</u>  | 0<br>       | <br>0                    | <br>0 | 8-FA  | 1-на   |

|                    | 0 0                                                   | 0          | <br>0 |     | °      | <u>.</u>  | 0<br>       | 0<br>- <del></del>       | 0<br> | CLA   |        |

| 10                 | 8 9                                                   | 7          | 6     | 5   | 4      | 3         | 2           | 1                        | 0     |       |        |

|                    | Stages<br>FAs<br>HAs<br>Gates<br>CLA<br>CPU Time (ns) |            |       |     |        |           |             | 4<br>44<br>4<br>68<br>10 |       |       |        |

| CFO TIME (III) 230 |                                                       |            |       |     |        |           |             |                          |       |       |        |

∃a)

(b)

Figure 1. CSA network for M=8 and n=8. (a) Logic synthesis. (b) Circuit layout.

SPAN V1.00

• 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 10 9 8 7 6 5 4 3 2 1 0

(a)

(b)

Figure 2. CSA network for M=5 and n=8. (a) Logic synthesis. (b) Circuit layout.