### IMPLEMENTATION OF THE SINGLE MODULUS COMPLEX ALU

Rom-Shen Kao Fred J. Taylor

### University of Florida

**ABSTRACT**

Recently the complex residue number system, or RNS, has been a subject of intense study. One special embodiment of this theory is the single modulus complex RNS processor which suggests both implementation and performance advantages. In this paper these conjectures are tested in the context of a CMOS gate array design and are found to be valid.

This work was supported under an ARO grant.

#### I. INTRODUCTION

Over the past several years there has appeared numerous articles advocating the use of the quadratic residue number system or QRNS, for performing complex algebraic operations [1-6]. As a subset of the more general theory of the residue number system (RNS), it has been shown to offer low multiplication complexity but, like other RNS tools, suffers from an inability to efficiently service scaling, magnitude comparison, or number system conversion calls. In an attempt to overcome this objectionable feature, the single modulus QRNS, or SM-QRNS was proposed [6]. Based on Fermat primes p =  $2^{11}$  + 1 for n =  $2^{11}$ , the SM-QRNS was shown to offer several advantages over other QRNS embodiments. They were:

i compared to the general ORNS

- scaling greatly simplified

- magnitude comparison greatly simplified

- sign detection trivial

- capable of assimilating existing high performance

radix-2 hardware into its design

- ii compared to the RNS and conventional binary weighted systems

- reduced computational complexity

- reduced computational latency

# II. THE SM-QRNS

Let  $Z_{D}[i] = \{a+ib \mid a,b \in Z_{D}; i = SQRT(-1)\}$ . The ring  $Z_{D}[i]$  is called the ring of Gaussian integers modulo p. A complex CRNS number of the form a+ib evaluates to i if a=0 and b=1. If  $i \notin Z_{D}$ , then it is considered to be **imaginary**. That is, there is no  $i \in Z_{D}$  such that  $i^{2}=-1$  mod p and i is historically called a <u>nonquadratic root</u> and -1 is a <u>quadratic root</u> and a+ib is

real. For example, if p = 17 and i = 4  $\epsilon$  Z<sub>p</sub>, then i<sup>2</sup> = 16  $\epsilon$  -1 mod 17. For such moduli the concept of an imaginary operation is void. Now define Z<sub>(p,p)</sub> = Z<sub>p</sub> x Z<sub>p</sub> and (a, b), (c, d)  $\epsilon$  Z<sub>(p,p)</sub> with rules of composistion given by:

addition:

$$(a,b) + (c,d) = ((a + c) \mod p, (b + d) \mod p)$$

multiplication:

$(a, b)(c, d) = (ac \mod p, bd \mod p)$  (1)

Even though addition requires two (2) real adds (as in the CRNS), multiplication requires but two (2) real multiplies (versus 4 products and 2 adds in the CRNS)! The isomorphism between  $Z_p[i]$  and Z(p,p) has been well studied and for p a Gaussian prime satisfying p=4k+1 (in fact, it can be a product of Gaussian primes). The isomorphism given by  $\phi$ , maps a complex number c=a+ib (i=SQRT(-1)) into a two tuple  $(z,z^*)$  as follows:

$$(a, b) \longleftrightarrow (z, z^*)$$

$$z = (a + jb) \mod p;$$

$$z^* = (a - jb) \mod p;$$

$$j^2 \equiv -1 \mod p; \ j \in Z_p$$

$$a = 2^{-1}(z + z^*) \mod p;$$

$$b = (2j)^{-1}(z - z^*) \mod p$$

$$(2)$$

In (2), j denotes a quadratic root. In fact there are two such roots (say  $\mathbf{j}_1$  and  $\mathbf{j}_2$ ) which are both additive and multiplicative inverses of each other.

A specific choice of Gaussian primes are those which are also Fermat primes of the form  $p=2^n+1$ ,  $n=2^m$ , n=2, 4, 8, 16. For the case where n=32, p is a composite Gaussian prime and therefore also an admissable modulus. As such, the critical parameters found in equation 2 take the form:

$$2^{-1} = 2^{n-1} + 1$$

;  $j = 2^{n/2}$ ;

$j^{-1} = 2^n + 1 - 2^{n/2}$  (3)

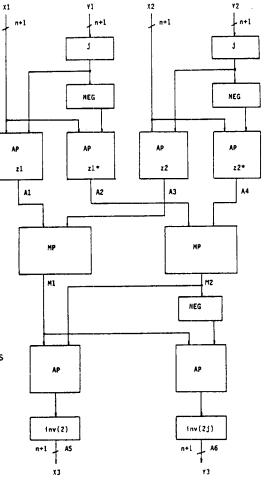

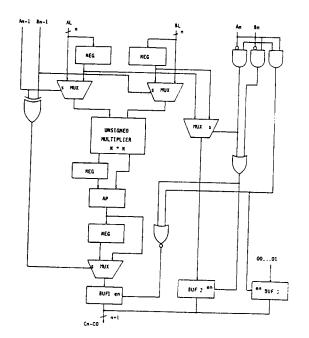

which can be seen to be the essentially radix 2 scaling operations. Based on this result, a SM-QRNS of the type suggested in Figure 1 can be designed. The functional elements will be summarized in the next section.

# III. SM-QRNS ARCHITECTURE

The SM-QRNS unit suggested in Figure 1 consists of the following function modules.

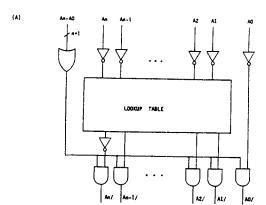

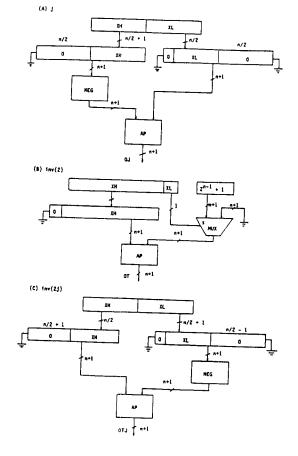

i) Negator (see Figure 2): Note,  $-x = (p - |x|) \mod p = 2^n + 2 + x) \mod p$  where x denotes bitwise complement of x. Then if  $x = \sum a_1 2$  it follows that  $-x = \sum b_1 2$  where:

$$b_{0} = \overline{a_{0}}$$

$$b_{1} = \overline{a_{1}}$$

$$b_{2} = \overline{a_{1}}^{a_{2}} + a_{1}\overline{a_{2}}$$

$$\vdots$$

$$b_{n} = \overline{a_{1}} \overline{a_{2}} \cdots a_{n}$$

$$+ (a_{1} + a_{2} + \cdots + a_{n-1})\overline{a_{n}}$$

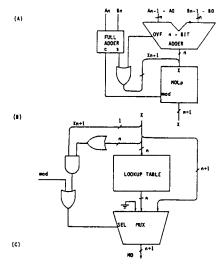

ii) Modulo p Adder (see Figure 3): The mod p adder consists of an n-bit fast carry-lookahead adder, a modulo p mapping unit, and control logic (compare network). The mapping unit is designed to transfer S = A + B into V = (A + B) modp or V = S - p if S > p, using the following procedure [7]:

a. Starting with the LSB of S, complement all "O's" up to the first encountered "1.

b. Complement the first encountered "1." bits of c. Leave all other

greater significancy unchanged.

More specifically,

$$v_{0} = \overline{s_{0}}$$

$$v_{1} = s_{0}s_{1} + \overline{s_{0}} \overline{s_{1}}$$

$$v_{2} = \overline{s_{0}} \overline{s_{1}} \overline{s_{2}} + (s_{0} + s_{1})s_{2}$$

$$\vdots$$

$$v_{n-1} = \overline{s_{0}}\overline{s_{1}} \cdots \overline{s_{n-1}} + (s_{0} + s_{1} + s_{n-2})s_{n-1}$$

$$v_{n} = 0$$

iii) <u>Modulo p Multiplier</u> (see Figure 4): The modulo p multiplier consists of an unsigned multiplier and a network to process some exceptions:

a. If both inputs equal 2<sup>n</sup>, then set the product to 1.

b. If only one input equals  $2^n$  (say A) then set the product to -B

# IV. SM-QRNS SUPPORT

The SM-QRNS architecture displayed in Figures 1 through 4 consists of a number of common They are summarized macrocells called modules. below and shown in Figure 5.

a. Scaling by

$$j(eq. 3)$$

$jX \mod p = 2^{n/2}X_{LO} - X_{HI}$ ,

$X = 2^{n/2}X_{HI} + X_{LO}$

b. Scaling by

$$2^{-1}$$

(eq. 3)

$2^{-1}$  X mod p =  $(2^{n-1} + 1)$  X<sub>LO</sub> + X<sub>HI</sub>;

x =  $2$ X<sub>HI</sub> + X<sub>LO</sub>

c. Scaling by

$$(2j)^{-1} (eq._3)/(2-1) \chi_{L0}$$

;  $\chi = 2^{(n/2+1)} \chi_{HI} + \chi_{L0}$

# V. SM-QRNS GATE ARRAY DESIGN

The SM-QRNS architecture reported in the previous section were tested using TEGAS (TEst Generation And Simulation language) and the IGC20000 Macro Library which are parts of the GE Semiconductor Gate Array design tool kit. Each array cell consists of three CMOS devices using 2 micron gate-length and the array itself may consist of up to 54,000 internal transistors. With these building blocks, the following modules were designed:

MUTT: Product modulo p NEG: Negates modulo p

scale by j SUM: Carry lookahead adder JX:

ITWO: scale by  $2^{-1}$ MDL: Sum modulo p

ITWOJ: scale by  $(2j)^{-1}$ MUL: Carry-save unsigned multiplier

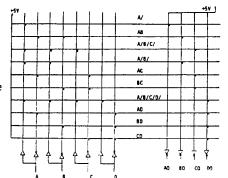

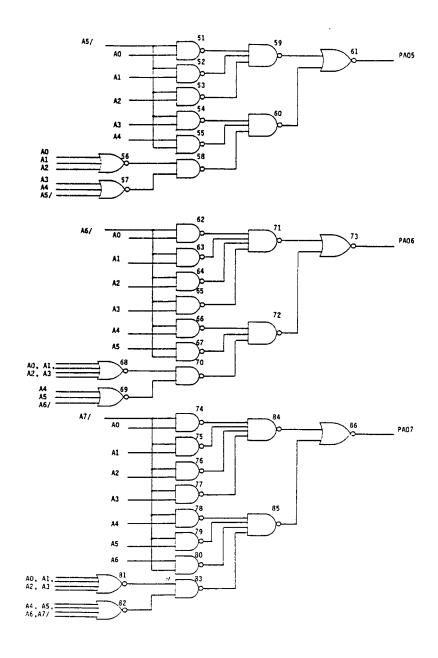

For expository reasons, the MDL module will be developed more fully. The MDL accepts data from the adder and modifies the received data modulo p if S > p or passes it unaltered otherwise. A section of this logic is reported in Figure 6. Such data is used to define the gate array.

## VI. ARRAY ANALYSIS

The macros used to configure the SM-QRNS are 2, 3, 4, and 5 input NAND gates, 2 input XOR and XNOR gates, 2, 3, and 4 input NOR gates, 2-2 and 2-2-2 AND-OR- inverters. The NEG, SUM, MDL, MUL, MUTT, JX, ITWO, and ITWOJ units were designed and integrated into a SM-QRNS machine. An eight bit design, for example, consists of 4187 1/3 array cells where each array cell consisted of 3 p-n channel transistors pairs.

The main purpose for this study was to develop a peformance database for SM-QRNS and conventional CRNS designs. To establish a common denominator for comparison, the QRNS and CRNS units are configured so as to have a similar hardware budget with both operating dual modulo p multipliers (see Figure 1). The basic database used to support the comparative analysis is reported in Table 1.

Assume  $T_c$  is the carry propagation time and  $T_s$ is the sum propagation time for a one-bit adder. The timing analysis for the module MUL unit, in general case is

$$T_{d} = \{ (n-1)T_{S} + (n-1)T_{C} & \text{if } nT_{C} < (n-1)T_{S} \}$$

$$if nT_{C} > (n-1)T_{S} \}$$

where n is the bit number of the multiplicands. Based on the equivalent hardware budget assumption, the timing analysis for the QRNS and CRNS systems are stated as follows:

- a. Because of the number of gate levels are the same for the case where n = 8 to 16, assume that the gate delay time for the nonwordlength dependent modules (i.e., nonmultiplier) is fixed.

- b. Assume  $T_c = T_S$ , the delay time  $T_m$  for the single modulus multiplier MUTT is  $T_m = (2n-2)T_c + 230ns$

- c. The delay time for the QRNS system under worse case is  $T_{\rm d} = T_{\rm m} \, + \, ({\rm delay \ time \ of \ non-processing \ units})$

$$= (2n - 2)T_C + 230ns + 650ns$$

$$= 2nT_c - 2T_c + 880ns$$

while the delay time for CRNS system under worse case is

$T_x = 2T_m + (delay time of non-multiplier units)$

$$= 2((2n - 2)T_c + 230ns) + 200ns$$

$$= 4nT_c - 4T_c + 660ns$$

The "break even" wordlength is given by  $4nT_C - 4T_C + 660ns = 2nT_C - 2T_C + 880ns$   $2nT_C^c - 2T_C^c = 220ns$

From the performed simulation,  $T_c$  approximates 15ns. Therefore, the equation shown above becomes reduced to 30n = 190 or n = 6.3.

Based on the timing studies and data reported in Table 1, the performance of a CRNS and SM-QRNS can be compared. The data represents temporal bounds on the performance of each individual module. For both the SM-QRNS and CRNS it can be seen that the principal bottleneck is at the multiplier level. The table also reports summary data for the integrated SM-QRNS and CRNS designs. This data was produced using TEGAS applied to a complete design rather than simply summing the individual module delays (in accordance to Figure 1). The result is a superior SM-QRNS design.

## V. SUMMARY AND CONCLUSIONS

The principal objective of this work was to test the recently published conjecture that an integrated QRNS based unit could outperform an CRNS counterpart. Based on the analysis provided, using relatively slow gate array technology, the conjecture has been verified. While the results will vary somewhat as a function of technology and macro-cell differences, the reported results do represent an unbiased exploration of SM-QRNS question using accepted analysis tools. The foregone analysis indicates that in order to increase the potential speed advantage of SM architecture, the non-wordlength dependent overhead factors (i.e. scaling, negation and mod p) should be reduced to a minimum. It is noted that using

gate-level constructs to implement these modules will present penalties. For example, moving from one fan-out to three could easily add another 1.06ns delay for the ND5 macro (5-input NAND gate) under 27°C and 5 V operating conditions. Instead, it may be advantageous to use a high-performance commerically available multiplier chip (used as an attached coprocessor) or high speed semiconductor table lookup (for n < 12 bits). For example, a 45ns 16 x 16 multiplier chip could be interfaced to a SM-QRNS controller/engine. It would accept operands from the engine, compute the binary weighted product, and return the results to the engine for modulo p reduction. The table-lookup method would also be a suitable forum in which to develop a faster architecture. For example, using high speed memory device (e.g., 40ns, 64kx1 static RAM chips) to implement the mapping logic in a n = 16 QRNS system, the following latencies have been

| Table-Lookup |                                 | Gate Array                      |

|--------------|---------------------------------|---------------------------------|

| NEG          | 40ns                            | 60ns                            |

| SUM + MDL    | 250ns                           | 250ns                           |

| JX           | 40ns                            | 130ns                           |

| ITWO         | 40ns                            | 100ns                           |

| ITWOJ        | 40ns                            | 120ns                           |

| MUTT         | (2n-2)T <sub>C</sub><br>+ 230ns | (2n-2)T <sub>a</sub>            |

|              | + 230ñs                         | (2n-2)T <sub>c</sub><br>+ 230ns |

Using the fast lookup method, the non-wordlength overhead bias to  $T_q$  can be decreased from 880ns to 670ns. The "break even" wordlength then becomes n = 1.3.

Some large and varied macrocell libraries, composed of input more pin gates, multiplexers, register files, and multipliers, are available in the market place. These predefined LSI/VLSI functions are optimized such as the C20000 CMOS gate array from Fujitsu Microelectronics mixes high-speed static memory with random logic. This configuration, which consists of 15,000 uncommitted gates with 6K or 12K bits of RAM, provides both small lookup table and discrete logic design capabilities. The bipolar array is another choice for modular design although it has fewer gates within a single chip (up to 8,000 gates versus 20,000 for CMOS counterparts). Higher speed with fewer problems in driving large fan-out (as many as eight loads) can be found in bipolar arrays which have advantages in designing high throughput signal processing systems.

### REFERENCES

- M.C. Vanwormhoudt, "Structural properties of complex residue rings applied to number theoretic Fourier transforms," <u>IEEE Trans.</u> <u>Acoust., Speech, Signal Processing</u>, Vol. ASSP-26, Feb. 1978.

- S.H. Leung, "Application of residue number system to complex digital filters," in Proc. 15th Asilomar Conf. Circuits Syst. Comput., Pacific Grove, CA, Nov. 1981, pp. 70-74.

- 3. J.B. Krogmeier and W.K. Jenkins, "Error detection and correction in quadratic residue number system," in Proc. IEEE 26th Midwest Symp. Circuits Syst., Pueblo, MX, Aug. 1983.

- 4. M.A. Soderstrand and G.D. Poe, "Applications of a quadratic-like complex residue arithmetic system to ultrasonics," in <a href="Proc. 1984 ICASSP">Proc. 1984 ICASSP</a>, San Diego, CA, Mar. 1984.

- F. Taylor et al., "A radix-4 FFT using complex residue arithmetic," <u>IEEE Trans. Comput.</u>, June 1985.

- 6. F Taylor, "Single modulus complex ALU," <u>IEEE</u> <u>Trans. on ASSP</u>, Oct. 1985, pp. 1302-1315.

- F. Taylor, "Residue arithmetic: A tutorial with examples," IEEE Computer Magazine, May 1984.

Acknowledgement: To JoEllen Wilbur for her assistance.

This work was supported under an ARO grant.

Figure 1 Functional block of the Single Modulus QRNS (SM-QRNS) unit

| Table I    |             |            |      |       |      |  |  |  |

|------------|-------------|------------|------|-------|------|--|--|--|

| Listing of | propagation | delay of   | the  | CRNS, | QRNS |  |  |  |

|            | system and  | their modu | ıles |       |      |  |  |  |

| Modulus P = 2 <sup>n</sup> + 1<br>Delay time | n = 4 |       |       | n = 8  |        | n = 16 |  |

|----------------------------------------------|-------|-------|-------|--------|--------|--------|--|

| Module                                       | min   | max   | min   | max    | mi n   | max    |  |

| NEG                                          | 30ns  | 50ns  | 40ns  | 60ns   | 40ns.  | 6Uns   |  |

| SUM                                          | 60ns  | 70ns  | 120ns | 130ns  | 120ns  | 130ns  |  |

| MDL                                          | 50ns  | 80ns  | 70ns  | 120ns  | 70ns   | 120ns  |  |

| MUL                                          | -     | 80ns  | 230ns | 240ns  | 540ns  | 560ns  |  |

| MUTT                                         | -     | 250ns | 300ns | 470ns  | 620ns  | 790ns  |  |

| JX                                           | 70ns  | 110ns | 90ns  | 130ns  | 90ns   | 130ns  |  |

| ITWO                                         | 50ns  | 60ns  | 80ns  | 100ns  | 80ns   | 100ns  |  |

| ITWOJ                                        | 70ns  | 100ns | 90ns  | 120ns  | 90ns   | 120ns  |  |

| QRNS                                         | 480ns | 740ns | 900ns | 1100ns | 1220ns | 1420ns |  |

| CRNS                                         | 230ns | 560ns | 910ns | 1200ns | 1550ns | 1840ns |  |

(8)

Figure 2 (A) Circuit diagram of the NEGATOR module (B) PLA implementation of a 4-bit lookup table for the NEGATOR module

A/B 44/ ABC/ A/C 9/C ABCD/ A/0 8/D C/B

AO = A/ BO = A/8+AB/ CO = ABC/ + (A/+B/)C DO = ABCD/ + (A/+B/+C/)D

Figure 3

- (A) Modulo P Adder(B) MDL<sub>p</sub> unit implemented by using the table lookup method

- (C) PLA implementation of a 4-bit lookup table for the  $\mathsf{MDL}_p$

80 • AB+A/8/ CO - A/8/C/ + (A+8)C 00 - A/8/C/0/ -{A+8+C)D

A0 - A/

Figure 4 Modulo P Multiplier

Figure 6 Circuit diagram of the MDL module (a submodule of Modulo P Adder)