#### ARITHMETIC FOR VECTOR PROCESSORS

R. Kirchner and U. Kulisch

Fachbereich Informatik, Universität Kaiserlautern Fakultät für Mathematik, Universität Karlsruhe West Germany

Abstract: In electronic computers the elementary arithmetic operations are these days generally approximated by floating-point operations of highest accuracy. Vector processors and parallel computers often provide additional operations like "multiply and add", "accumulate" or "multiply and accumulate". Also these operations shall always deliver the correct answer whatever the data are. The user should not be oblighed to execute an error analysis for operations predefined by the manufacturer.

In the first part of this paper we discuss circuits which allow a fast and correct computation of sums and scalar products making use of a matrix shaped arrangement of adders and pipeline technology. In the second part a variant is discussed which permits a drastic reduction in the number of adders required. The methods discussed in this paper can also be used to build a fast arithmetic unit for micro computers in VLSI-technology.

### 1. Introduction

Modern computers of highest performance, so-called vectorprocessors or supercomputers, are gaining considerably in importance in research and development. They serve for simulation of processes which cannot be measured at : .1 or only with great effort, for solving large en incering design problems or for evaluation of large sets of measured data and for many other applications. It is commonly assumed that these competers open a new dimension for scientific comput tion. In sharp contrast to this is the fact that the arithmetic implemented on supercomputers differs only marginally from that of their slower predecessors, although results are much more sensitive to rounding errors, numerical instabilities, etc. due to the huge number of operations executes

Research in numerical mathematic with a more comprehensive and arithmetic, reliable results can obtained when dealing with extens blems. Computers with this kind proved the significance of this many successful applications.

Until now, it has been assumed that an optimal vector arithmetic could not be implemented on supercomputers. The users, therefore, had to choose between either lengthy computation times and accu-

rate results on general purpose computers or comparatively short computation times and possibly wrong results obtained on supercomputrs.

It was assumed, in particular, that correct computation of continued sums and scalar products, which are necessary for vector arithmetic, could not be implemented on supercomputers with pipeline processing. Well known circuits, which solve this problem, require several machine cycles for carrying out a single addition whereas a computer of highest performance with traditional arithmetic

carries out one addition in each cycle<sup>1</sup>. This paper describes various circuits for the optimal computation of sums and scalar products at the speed of supercomputers. There is, in principle, no longer any reason to continue to accept inaccurate sums or scalar products by not using optimal vector arithmetic on vectorprocessors and supercomputers. The additional costs compared with the cost of the complete system are justified in any case. It takes the burden of an error analysis from the user.

The first electronic computers were developed in the middle of this century. Before then, highly sophisticated electromechanical computing devices were used. Several very interesting techniques provided the four basic operations of addition, subtraction, multiplication, and division. Many of these calculators were able to perform an additional operation which could be called "accumulating addition/subtraction" or continued summation. The machine was equipped with an input register of about 10 to 13 digits. Compared to that, the result register was much longer and had perhaps 30 digits. It was situated on a sled which could be shifted back and forth relatively to the input register. This allowed an accumulation of a large number of summands into different positions of the result register. There was no rounding executed after each addition. As long as no overflow occurred, this accumulating addition was error free. Addition was associative, the result being independent of the order in which the summands were added.

This accumulating addition without intermediate roundings was never implemented on electronic com-

By a cycle time or a machine cycle we understand the time which the system needs to deliver a summand or a product, in case of a scalar product computation, to the addition pipeline.

puters. Only recently, several /370 compatible systems have appeared which simulate this process on general purpose machines by accumulating into an area in main memory, which is kept in the cache memory for enhanced performance. [5], [6]. This allows the elimination of a large number of roundings and contributes essentially to the stability of the computational process. This paper desribes circuits for an implementation of the accumulating addition on very fast computers making use of pipelining and other techniques.

The first <u>electronic computers</u> executed their calculations in fixed-point arithmetic. Fixed-point addition and subtraction is error free. Even very long sums can be accumulated with only one final rounding in fixed-point arithmetic, if a carry counter is provided which gathers all intermediate positive or negative overflows or carries. At the very end of the summation a normalization and rounding is executed. Thus accumulation of fixed point numbers is associative again. The result is correct to one unit in the last figure and it is independent of the order in which the summands are added. Fixed-point arithmetic, however, imposed a scaling requirement. Problems needed to be preprocessed by the user so that they could be accommodated by the fixed-point number representation. With the increasing speed of computers, problems that could be solved became larger and larger. The necessary pre-processing soon became an enormous burden.

The introduction of floating-point representation in computation largely eliminated this burden. A scaling factor is appended to each number in floating-point representation. The arithmetic itself takes care of the scaling. Multiplication and division require an addition, respectively subtraction, of the exponents which may result in a large change in the value of the exponent. But multiplication and division are relatively stable operations in floating-point arithmetic. Addition and subtraction, in contrast, are troublesome in floating-point.

As an example let us consider the two floatingpoint vectors

$$\mathbf{x} = \begin{bmatrix} 10^{20} \\ 1223 \\ 10^{24} \\ 10^{18} \\ 3 \\ -10^{21} \end{bmatrix} \qquad \mathbf{y} = \begin{bmatrix} 10^{30} \\ 2 \\ -10^{26} \\ 10^{22} \\ 2111 \\ 10^{19} \end{bmatrix}$$

A computation of the inner or scalar product of

these two vectors gives

$$x.y = 10^{50} + 2,446 - 10^{50} + 10^{40} + 6,333 - 10^{40} = 8,779$$

Most digital computers will return zero as the answer although the exponents of the data vary only within 5 % or less of the exponent range of large systems. This error occurs because the floating-point arithmetic in these computers is unable to cope with the large digit range required for this calculation.

Floating-point representation and arithmetic in computers was introduced in the middle of this

" about 100 floating-point operations a sec of The fastest computers today are able to execute billions of floating-point operatio: in a cond. This is a gigantic gain in factor of  $10^7$  over the electronic comspeed by the  $\epsilon$  mly fifties. Of course, the probputers o lems tha can be dealt with, have become larger and large. The procion is whether floating-point represent tion an arithmetic which already fails in simple calculations, as illustrated above, are still adequate o be used in computers of such gigantic speed for huge problems. We think hat the set of floating-point operations extende, by a fifth operation, the "acshould be cumulatir. addition/subtraction" without intermediate rounding, an operation which was already available on ma. electromechanical calculators. purpose of this paper to show that this It is the additiona. opera ion can be executed with extreme speed. W realize this operation by adding the floatingint samends into a fixed-point number over the ull fleating-point range. Thus "accumulating ac ition/subtraction" is error free. Even very long chains of additions/subtractions can be executed with only a single rounding at the very end of the summation. Such "Accumulating addition/ subtracti " is sociative. The result is inde-

centry. Commute then were relatively slow, being

able to 🕝

cute c

With the ifth coration "accumulating addition/subtractin", we combine the advantages of fixedpoint ar hmetic - error free addition and subtraction ven fo: very long sums - with the advantages of floating-point arithmetic - no scaling requireme ts.

the order in which the summands are

# The tate of the Art

pendent (

<u>added</u>.

A normalized floating-point number z (in sign-magnitude representation) is a real number of the form

$$z = * m \cdot b^e$$

Here  $\star \in \{+,-\}$  denotes the sign (sign(z)), m the mantissa mant(z)), b the base of the number system and  $\epsilon$  the exponent (exp(z)). b is an integer number with b > 1. The exponent is an integer and lies between two integers e1 ≤ e2. In general, e1  $\langle$  0 and  $\epsilon$   $\rangle$  0. m is the mantissa. It is of the form

$$m = \sum_{i=1}^{l} z[i] \cdot b^{-i}.$$

Here, the z[i] denote the digits of the mantissa;  $z[i] \in \{0,\overline{1},\ldots,b-1\}$  for all i = 1(1)n and z[1]≠ 0. 1 is the length of the mantissa. It denotes the number of mantissa digits carried along. The set of normalized floating-point numbers does not contain t'e number 0. In order to obtain a unique definition of 0 one can additionally define: sign(0) = +, mant(0) = .000 ... 0 (1 zeros afterthe point) and exp(0) = e1. This kind of floatingpoint system depends on four constants b, l, el and e2. We denote it with S = S(b,l,e1,e2). Let

$$\mathbf{u} = (\mathbf{u}_{i}) = \begin{bmatrix} \mathbf{u}_{1} \\ \mathbf{u}_{2} \\ \vdots \\ \mathbf{u}_{n} \end{bmatrix} \qquad \mathbf{v} = (\mathbf{v}_{i}) = \begin{bmatrix} \mathbf{v}_{1} \\ \mathbf{v}_{2} \\ \vdots \\ \mathbf{v}_{n} \end{bmatrix}$$

be two vectors, the components of which are normalized floating-point numbers, i.e.  $\mathbf{u}_i$ ,  $\mathbf{v}_i \in S$  forall  $\mathbf{i} = \mathbf{i}(1)\mathbf{n}$ . The theory of computer arithmetic[1], [2], [3] demands that scalar products of two floating-point vectors  $\mathbf{u}$  and  $\mathbf{v}$  be computed with maximum accuracy by the computer for each relevant, finite  $\mathbf{n}$  and different roundings. By doing so, millions of roundings can be eliminated in complicated calculations. This contributes essentially to the stability of the computational process and enlarges the reliability and accuracy of computed results. Furthermore, defect correction then becomes an effective mathematical instrument.

This requires, fer example, the execution of the following formula: by the computer:

$$\mathbf{u} \odot \mathbf{v} = \bigcirc \left( \sum_{i=1}^{n} \mathbf{u_i} * \mathbf{v_i} \right)$$

$$\mathbf{u} \odot \mathbf{v} = \bigcirc \left( \sum_{i=1}^{n} \mathbf{u_i} * \mathbf{v_i} \right)$$

$$\mathbf{u} \nabla \mathbf{v} = \bigcirc \left( \sum_{i=1}^{n} \mathbf{u_i} * \mathbf{v_i} \right)$$

$$\mathbf{u} \nabla \mathbf{v} = \bigcirc \left( \sum_{i=1}^{n} \mathbf{u_i} * \mathbf{v_i} \right)$$

$$\mathbf{u} \nabla \mathbf{v} = \bigcirc \left( \sum_{i=1}^{n} \mathbf{u_i} * \mathbf{v_i} \right)$$

$$\mathbf{u} \nabla \mathbf{v} = \bigcirc \left( \sum_{i=1}^{n} \mathbf{u_i} * \mathbf{v_i} \right)$$

$$\mathbf{u} \nabla \mathbf{v} = \bigcirc \left( \sum_{i=1}^{n} \mathbf{u_i} * \mathbf{v_i} \right)$$

$$\mathbf{u} \nabla \mathbf{v} = \bigcirc \left( \sum_{i=1}^{n} \mathbf{u_i} * \mathbf{v_i} \right)$$

$$\mathbf{u} \nabla \mathbf{v} = \bigcirc \left( \sum_{i=1}^{n} \mathbf{u_i} * \mathbf{v_i} \right)$$

$$\mathbf{u} \nabla \mathbf{v} = \bigcirc \left( \sum_{i=1}^{n} \mathbf{u_i} * \mathbf{v_i} \right)$$

$$\mathbf{u} \nabla \mathbf{v} = \bigcirc \left( \sum_{i=1}^{n} \mathbf{u_i} * \mathbf{v_i} \right)$$

$$\mathbf{u} \nabla \mathbf{v} = \bigcirc \left( \sum_{i=1}^{n} \mathbf{u_i} * \mathbf{v_i} \right)$$

$$\mathbf{u} \nabla \mathbf{v} = \bigcirc \left( \sum_{i=1}^{n} \mathbf{u_i} * \mathbf{v_i} \right)$$

right side denote the correct multiplication and

addition for rear numbers. O,  $\square$ ,  $\nabla$ ,  $\triangle$  are rounding symbols. O denotes a rounding to the nearest floating-point number,  $\square$  denotes the rounding towards zero,  $\nabla$  denotes the monotone downwardly directed rounding and  $\triangle$  denotes the monotone upwardly directed rounding. For an execution of formula (I) first the products  $\mathbf{u}_i \to \mathbf{v}_i$  have to be correctly calculated by the computer. This leads to a mantissa of 21 digits and an exponent which lies in the range of  $2e\mathbf{1}-1\leq 2e\mathbf{v}$ . So the computation of evaluar products is reduce. To the evaluation of evaluar of the following for

$$\diamondsuit \ (\sum_{i=1}^{\Sigma} w_i), \quad n \in \mathbb{N}$$

(II)

Here the weare floating-point numbers of double length  $\mathbf{w}_i$  (4.21, 4.1-1.2e2), for all i=1(1)n.  $\diamondsuit$  denotes a general counding pubol,  $\diamondsuit \in \{\emptyset, \square, \nabla, \Delta\}$ , assures have to be taken first to generate and correspond to the seminarity  $\mathbf{w}_i$  correctly in the computation. In see of scalar products this can be done by some for and  $\mathbf{w}_i$  and  $\mathbf{w}_i$  are includes. For tradition of the seminarity powers computers there

are several ways to correctly compute (I) and (II) mentioned in the literature. It is the intention of this paper to describe circuits for high speed computation of (I) and (II) on vector computers by means of pipeline techniques. These circuits have to accept and process one summand from (I) resp. (II) during each machine cycle. To assist in the understanding of the following material, we first refer to one of the possibilities mentioned in [4]:

We consider a register of  $L = k + 2e^2 + 2l + 2|e^1|$  digits of base b, which should be placed in the arithmetic unit (Figure 1).

| k   | 2e2 | 21 | 2 e1 |

|-----|-----|----|------|

| Ъ—— |     |    | L    |

Figure 1

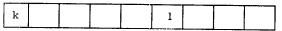

We divide this register into segments of length 1 (Fig. 2):

Figure 2

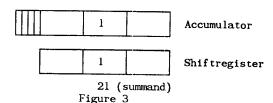

The summands in (I) and (II) are of length 21. They fit therefore, digitwise into a subrange of length 31 of this storage. This part of the register, which is determined by the exponent of the summand, is selected and loaded into an accumulator of length 31. The summand is loaded into a shiftregister of the same length, being correctly positioned according to the exponent, and then added into the accumulator (Figure 3).

The addition may produce a carry. In order to catch this carry, a few more digits than the three words of length 1 can be read from the long register into the accumulator, which is extended to the left accordingly. If not all of these digits are b-1, the carry is caught by these additional digits. Since it is possible that all these additional digits are b-1, a loop has to be provided which then adds the carry to the following digits of the long register. This loop may possibly have to be activated several times.

The addition of the summands of (I) resp. (II) into the long register, Fig. 1 resp. Fig. 2, may still produce a carry on the very far left of the register. In order to catch such carries the long register is extended on the left by a few more (k) digits of base b (Fig. 1). Then, any sum (I) or (II) of n summands can be added without loss of information into the long register of length L. bk carries may occur and can be processed without loss of information.

Here we conclude our description of one possibility to solve the problems (I) and (II). See [4].

What we just described belongs to the state of the

#### 3. Fast Computation of Sums and Scalar Products

The method described above is not suited for the computation of (I) resp. (II) on vector processors or supercomputers. The process of reading, shifting, carry handling, possibly by a loop, and writing back is certainly too slow to be executed in one cycle time of only a few nsecs of these computers. A solution of the problem by a very long adder is also very costly and probably too slow.

We therefore discuss here a variant of the possibilities mentioned above which makes processing of a summand of (I) resp. (II) possible within a very short cycle time. In comparison to general purpose computers, vector processors and supercomputers achieve their high speed of computation by means of pipeline technology whereby during each machine cycle a result is obtained. If scalar products and sums are to be computed with high speed on vector processors or supercomputers, one has to develop circuits which accept and process one summand (resp. a product) per machine cycle. This is only possible if the addition is done by means of pipeline technology. This paper describes various circuits which allow this.

At first the most important issues and ideas of the circuitry are presented in the text referring to Figures 4 to 15. These Figures contain some more details which are not essential for a first understanding of the principles. These details are presented later in chapter 4 "Additional Remarks concerning the Figures".

The circuit described below consists of a shifter which is followed by a pipelined adder called summing matrix (Figure 4). The shifting device may be realized by standard technology and belongs to the state of the art.

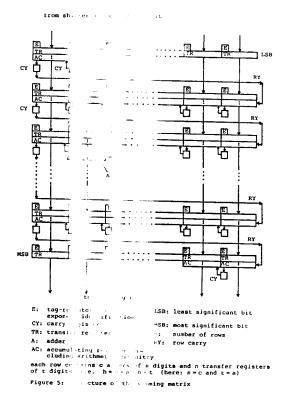

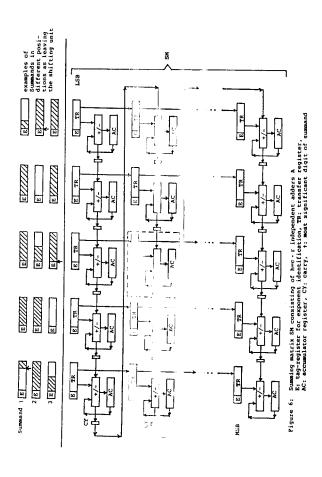

The adder consists of registers of a total length of S \( \) L. Here L denotes the length of the long register as outlined above<sup>2</sup> (Figure 1). The register length S is divided into r identical parts which are arranged as rows one below the other (Figure 5). r denotes the number of rows. All rows are of the same length. Each of these rows is divided into c > 1 independent adders A (see Figure 6). Thus the whole summing device consists of r . c independent adders. Each of these adders A has a width of a digits. Between two of these independent adders, carry handling must be possible. Also between the last adder of a row and the first one of the next row a carry handling must be possible. The complete summing device which we call the summing matrix SM, has a width of  $S = a \cdot c \cdot r di$ gits of base b. c denotes the number of columns of the summing matrix. It must be  $S \ge L = k + 2e^2 + 2l + 2 |e|$  (Figures 5, 6).

The summing matrix contains c · r independent adders A. Each of these adders must be able to add a digits of base b in parallel within one machine cycle, and to register a carry which possibly may occur. Since each row of the summing matrix con-

sists of c i adders, h:= c be added in ⊬ of t. sum of the r rc summiı mat: least as lon manti ъа 1. mands which : be add d. Ear summing matr: mracterized by nent corresp to the igit: upper right the summang mar least signini ligit, the low the summing : carries the r digit of the f daming device ( 6). Each summand a.ch product of must now be : ato the summir

proper positiselection 15 . of the expon-

the columns : bits of the . roughly with in two steps in

The incoming : shifted in t cross bar swi cording to th as a ringshif summand which serted at the ure 6 upper pa summand is di parts of wide. receives an ex specific digit one (Figures 5. also carry an and expanded so the summing mk row through th row in each ma.

ted as soon a

transfer regis

with the expoi. identification p mand. A summand, which arrives at the su remain connect after shifting position withi... he shifting unit. the addition is executed in only summing matrix. The shift procedur also cause an everhanging at the right end of the row. The overh ringshift at (see Figures 6 of both parts

neighbouring r of the summing atrix. If the most significate part of the summend, which was situated at the right end of the sl. fter, is added in row y then the addition of the east significant part, which was situated at te left end of

the shifter, is added in row y - 1. This means the next less significant row (see Figure 9). is, however, not at all neces ary that each

div denotes i ger division, i.e. 24 <u>di</u>  $\square = 2.$

ligits can 1 crix. Each nust be at f the sumit of the tain expotion. The arries the t part of significant e 5, Figure resp. (II)

rix at the rding to its e ...t. The row d by the more icant bits div h) and ···lection of ained by the 1-: gnificant t  $(exp \underline{d} h)$ n:s complies lection of the ing position

process descri

ls resp. produc

nifting unit (

into the corre

onents. The s

s means that

over the rig

end of the ship

sammands 2 and 3,

ibuted onto the

if the shiftregi:

.t identification

it, e.g. the 1e

and 10). The in

ment identifica.

nd now drops into

aming matrix, i

e cycle. The ad

: exponer t ider.

in the summing m

and thereafter

re now first el shifter, osition acis executed part of the .nd is reingister (Figigure 8). The independent r. Each part cording to a significant ual adders A . The shifted e top row of oceeds row by ing ahead one ion is execuication of a rix coincides t of the sum-

in Fig. 3.

ing unit. can the correct in this case, e row of the however, can ing part then is mainserted by a left end of the shifting unit 118). In this case, the addition the summand is t n executed in

$<sup>^{2}</sup>$  or a part of it. A reduction of the length S is discussed below.

mod denotes t remainder of integer division, i.e. 24 me = 10 = 4.

trated by the diagrams 12).

The addition may cause pendent adders A. Carry dependent adders absorb machine cycle these care. next more significant and a A, possibly together with another summand. machine cycle one summa: ming matrix, although summand may take sevethod displayed in the possibilities to handlcarry presencing or lo applied to speed up th one row. In any way, the carry processing to be the summations and in p that has to be done a summands or reading out In principle, the summi positive summands. Negr subtrahends are therefo. place not added but sut ries instead of positi to positive carries th sibly over e-veral mac. The independent adders additions as well as positive and negative ure 6, 12).

The design of the comp ing the summing matrix depend on the technological alreasy that the width A has to he osen in over the complete widt machi e cycle. Each re be at least as wide The shorter he rows can be shield into other hand, shortening the summing patrix in and with it, the numbe complete sullation pro After input of the I: read tarti:, with the vided the w in que carry har g. **In** t). have n bi ·noved. me is a path the throw ii natrix. the st and on : regis ars. aring th and corry and ling i may ill execut. reado . I ess the floa\* natt format can ( ) stored a able r. her proce sibi n be c

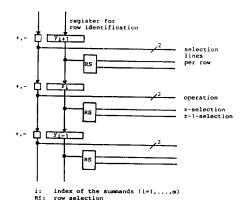

transfer unit carries a collete exponent identification. It is suffici at to identify the row by the exponent part exp d 'h of the summands in the shifter and to use it for selection of row y. The distinction whether the edition has to be executed in row y or in row : - 1 is made by a bit connected with each trans register or by a suitable column signal which distinguishes the transfer registers of a row. (The principle is illusown in Figures 11 and

> ries between the indeisters between the ine carries. In the next ; are added into the n this way, during each n be fed into the sumcarry handling of on .ochine cycles. The meres shows one of diverse carries. There may be d or other techniques rry processing within ming matrix allows the uted independently of el with the processing , e.g. adding further result.

ttrix can only process summands or positive rked and at the proper and. Here negative caries may occur. Similar at to be processed poscles. In other words: be able to carry out tions and to process s in both cases (Fig-

imming device containlescribed herewith can ed. 'e have mentioned the individual adders a way that an addition be executed within one he summing matrix must individual summands. e lister the summands ght position. On the width of the rows of s the number of rows pipeline steps for the

ma: the rows can be t significant row, prodoes not require any ise the carries first adour process can use ch the summands pass ne : sult rows follow t ugh the transfer ut process additions west significant rows ul ameously with the ing to the required : executed. The result te diate long vari-Sev ral rounding posout simultaneously as

mentioned in [4]. During the readout process the computation of a new scalar product resp. a new sum can be started.

The width a of the independent adders A depends on the technology used and on the cycle time of the system. The width should be as large as possible. But on the other hand, it must permit the addition over the a digits in one machine cycle. (In the case of a scalar product, a machine cycle is the time in which the system delivers a product).

Depending on the technology there are several possibilities of transportation of the summands to one of the r rows of the summing matrix SM.

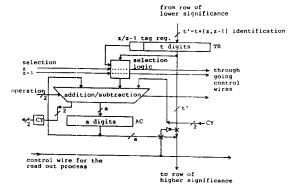

The method described above is based on the idea that each of the independent adders A is supplemented by a transfer register of the same width (plus tag-register for exponent identification and +/- control). During each machine cycle, each transfer register can pass on its contents to the transfer register in the corresponding position in the next row and receive a digit sequence from the transfer register in the corresponding position in the previous row. Attached to the transfer registers is the tag-register for exponent identification (Figure 5 and Figure 6). The contents of this register are always compared with the exponent identification of the corresponding adder. In case of coincidence, the addition resp. subtraction is activated (Figures 5, 6 and 12).

Alternatives to this procedure are also possible.

- One of these alternatives could be to transfer the summand in one machine cycle directly into the appropriate row of transfer registers of the summing matrix as determined by the exponent. During the following machine cycle, the addition is executed. Simultaneously, a new summand can be transferred to the same, or another row, so that an addition in each machine cycle is carried out.

- The procedure is similar to 1. The intermediate storage of the summands in transfer registers, however, is not necessary if it is possible to execute the transfer- and addition-process in one machine cycle. In this case, no transfer registers are necessary. The output of the result then also takes place directly.

- The transfer of the summands to the target row can be carried out not only sequentially and directly but also with several intermediate steps, for example, by binary selection.

Each one of these alternatives also allows a direct and therefore faster readout of the result without dropping step by step through the transfer registers.

To each independent adder A of length a belongs a transfer register TR which is basically of the same length. The number of adders A resp. transfer registers TR in a row is chosen in such a way that the mantissa length  $\bar{m}$  of the summands plus the length of the transfer registers t (=a) becomes less or equal to the length of the row  $(\bar{m} + a \le h)$ =  $c \cdot a$ ). In this way, an overlapping of the less significant part of the mantissa with its most significant part in one transfer register is avoided. For typical floating-point formats this condition may result in long rows of the summing matrix or in short widths a of the adders resp. transfer registers. The former case causes lengthy shifts while the latter case causes more carries (Figure 6 upper part and Figure 8).

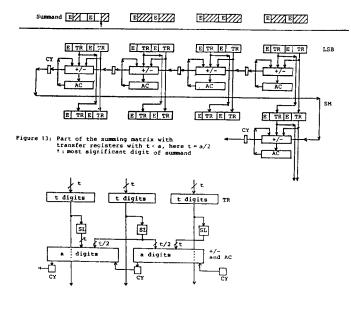

This disadvantage can be avoided by providing several ( $\geq$  2) partial transfer registers for each adder of length a. Each partial transfer register TR of length t  $\leq$  a carries its own exponent identification. Finally, the length t of the transfer registers can be chosen independently of the length a of the adders A. Both only need to be integer divisors of the row length of the summing matrix h = a • c = t • n (see Figures 13, 14 and 15).

Figures 6 and 13 show, in particular, that the summing matrix has a very systematic structure and that it can be realized by a few, very simple building blocks. It is suitable, therefore, for realization in various technologies.

Based on the same principle also, summands which consist of products of three and more factors can be added correctly.

If the summing matrix is to be realized in VLSI-technology it may happen that the complet summing matrix does not fit on a single chip. One should then try to develop components for the columns of the summing matrix since the number of connections (pins) between adjacent columns is much smaller than between neighbouring rows.

The following remarks and Figures 4 to 15 provide a more detailed description of the structure of the summing matrix and its functioning.

# 4. Additional Remarks concerning the Figures

The following abbreviations are used in the Figures:

- A Adder

- AC Accumulator Register

- CY Carry

- E Tag-Register for Exponent Identification

- LSB Least Significant Bit

- MSB Most Significant Bit

- SM Summing Matrix SR Shifter

- SR Shifter

- TR Transfer Register

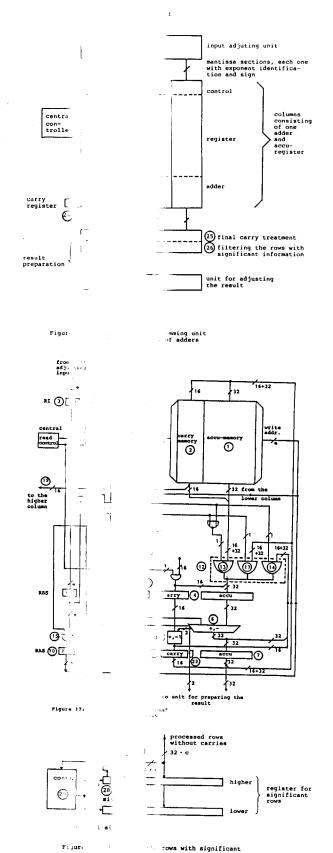

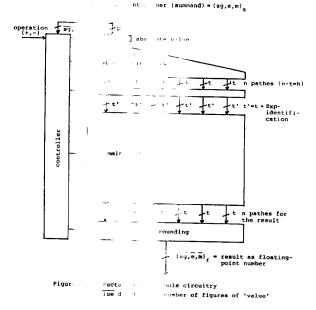

Figure 4 shows a structure diagram of the complete summing circuitry and illustrates the interaction of different parts of the whole circuitry, such as: separation of the summands into sign, exponent and mantissa, shifting unit, summing matrix, controller and rounding unit.

Figure 5: As mentioned in the text, we assume that S \( \) L. Figure 5 shows the case S \( \) L. There, for both the first and last rows part of the row is covered by transfer registers only. For the whole summing matrix this means that transfer registers exist for S digits but adders for L digits only. L is chosen such that it is a multiple of a. The dotted lines through the independent adders A indicate that the transfer wires bypass the adders. Above the transfer registers, the tag-register for exponent identification is indicated by a box. This register is part of the transfer register.

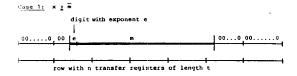

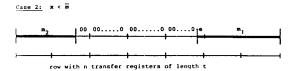

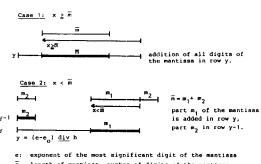

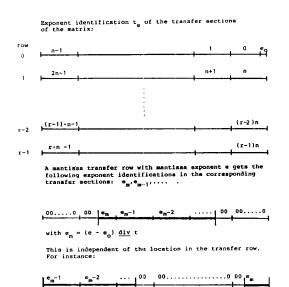

Figure 6 si. a block diagram e summing matrix. It is donas, is format which uses 4 bita ibe one di se b. Width of A. i bytes = Number of a.. in one row c Number of re n SM r = 8k = 20 carry.15, l = 14 dig. the mantissa e1 = -64 and **= 64.** Users of /3 tible sat recognize this data . → their dod; s.on format. L = 20 + 2 -2 • 14 + . • = -04 digits of 4 bits = 10. Width of the mplete summing maining  $S = a \cdot c \cdot$ = 4 • 5 • 8 lyte 0 bytes  $\geq$  L = 152 by tes. In this ex: the width t of cansfer registers equal: width of the ... t = a = 4bytes. The upper t of the Figure shows several positions of ...unds. Figure 7 def the exponent c mites x and y ∴e **sum**min ; mar of the dig horizontal, y vertical,. -> coordi (te btained according to Collowing formula denotes e reference poi e digit with the leexponent in t rix (at the upper t end). denote.. a least significa digit of the adder. denotes he most significat digit of theaddo-If the and the last rower the complete matrix ins adders over e full width then e,  $e_{\mathbf{0}}$  and  $e_{\mathbf{m}} = e_{\mathbf{0}} + \dots$ denotes e exponent of a digit to be added. e denotes e distance to the 'east significant end of : : matrix. (e-e<sub>0</sub>) th is the row co hate in which the dim vith the exponent of sadded. (e-e<sub>0</sub>) h indicates the distance to the least s. ficant end of row ;. Figures 8 a: describe the task of the shift unit and its clation to the generation of the lication which will be transferred exponent idea into the summ 5 matrix with the mantissa. The task of t shift unit is: adjust ratissa to the co... position for its add: on, if necessary bearing shift. emaining positions of the transfer fill the registe: resp. the row with meros. Figure 8 sho the shifted mantiset in both possible cases. Figure 9 desc bes the shift process. Two cases are to be dis guished: x = (e-e) $\mod h \ge m : no overlanging.$

whole mantissa is added in one

over anging,

ded

in

is

tì

$\mathbf{r}$

mantissa

$x < \bar{m}$ :

successive r s. Part  $m_1$  remains within the width of the row. The verhanging part m<sub>2</sub> is the left of the row. reinserted : . irnished with a cor-Both parts a penent identification. responding Part  $m_2$  wil. e selected for addition in row y-1 ereas part m<sub>1</sub> will be added in row y

The shifted and expanded a ntissa row drops row by row through the matrix as a transfer row. Before that, each transfer so tin is characterized by its exponent which carries the information where the addition has to be executed.

Figure 10 shows the exp identification of the sections of the trans: a transfer sections of transfer matrix co: is length t. Figure 10 da. es the exponent identification t (transfer c ment) of these transfer  $\boldsymbol{e}_{t}$  denotes the exponent sections of the matrix. of the e.g. least significant digit of a transfer

section then this canceler section can be characterized by the xpc ent identification te with  $\mathbf{t_e} = (\mathbf{e_t} - \mathbf{e_o}) \underline{c}(\mathbf{v})$ .

section of the sum . . . . tification. During this exponent identif: te. Equality trigg is . of Figure 10 shows ac summand get their empts A mantissa with the ex most significant di

Before a summand enter:

contact de de exponent of its oceives the exponent identific on (e - e $t = e_{m}$  in the most s ion, and exponent significant transit identific on e - 1 c - 2, etc. in the less

significal transfers Figure 10 clows in part the two typical cases. (A'lition c ⇒lete summand in one row resp. | two crass erows).

Figure 11 emplains the by row identification

is transfered through transferrey. The addition as the : identi:i coincide. he row two selection signa and it activate the adders of the row : questien activatin, ignal tion" if ... row index. A continati

"z-1-sele cont if y Then the transfer sect tion (z-1,1 -summat...: Since the transfer of values the information addition transf ...« Thus the ntrolle c with special conformation about to the struct of

`fied adder selection is row identification

matrix, each transfer

Wes an exponent iden-

re through the matrix,

... is then compared with

dilition. The lower part

....sfer sections of the

identification.

e matrix with the triggered off as soon and the row index switch RS generates Figure 12, too). An ia the wire "z-selecition equals the row is sent via the wire n ls the row index. ly carry the informa-

only contain positive tion or subtraction is

as transfer registers r each row which leads in Figure 11.

Figure 12 shows a block diagram for an adder cell. For simplicity the case t = a is selected. The cell contains centrally an "adder/subtractor" and a "partial accumulator section". The right upper corner shows the corresponding transfer register with wires from the next less significant row and to the next more significant row.

Additionally, the transfer register contains a tag register for "z/z-1" identification which indentifies through which selection wire the cell can be activated. The "adder/subtractor" receives the operands from the "partial accumulator section" and in case of selection from the transfer register. Zero is added if no selection takes place. In addition, the carry (positive or negative) arriving from the right is processed during each addition/subtraction and, if necessary, a carry is passed on to the next adder cell on the left. This carry is temporarily stored in an auxiliary register. Figure 15 further shows a control wire which selects the operation (addition/subtraction) as well as a control wire for the read out process (at the bottom of the figure). All control wires traverse the whole row.

Figure 13 is very similar to Figure 6. It shows one row of the summing matrix, but with t < a. The Figure is based on the same data format as Figure 6, i.e.: one digit of basis b is described by 4 bits, k = 20 carry digits, l = 14 digits in the mantissa, e1 = -64 and e2 = 64. Furthermore:

Width of AC: a = 4 bytes = 32 bits.

Number of adders in one row c = 4.

Number of rows in SM r = 10.

$L = 20 + 2 \cdot 64 + 2 \cdot 14 + 2 \cdot 64 = 304 \text{ digits per}$ 4 bits = 152 bytes.

Width of the complete summing matrix

$S = a \cdot c \cdot r = 4 \cdot 4 \cdot 10 \text{ bytes} = 160 \text{ bytes} \ge L =$ 152 bytes.

In this example the width of the transfer registers is smaller than the width a of the adders: t  $=\frac{a}{2}=2$  bytes.

This permits a smaller row width of only c = 4

The upper part of the Figure shows the position of a summand of  $\bar{m} = 2 \cdot l = 14$  bytes at a critical po-

Figure 14 shows another case where the width of the adders differs from that of the transfer registers (t \neq a). In the Figure the transfer registers are shown without exponent identification. Dotted lines again indicate transfer wires which bypass the adder in question.

Figure 15 shows a section of a row of the summing matrix with  $t \neq a$ . Here the case 3t = 2a has been selected. It shows how digits of the same transfer register are distributed and added into neighbouring adders.

## Summation with only one Row of Adders

We now discuss a further variant of the above circuitry for which adders exist only for one row of the summing matrix. The complete structure of this variant is similar to the one before (Figure 16). I.e. the complete circuitry consists of an input

adjusting unit, the summing unit with the actual accumulator and a device for carry handling, result row filtering and rounding.

The complete fixed-point word, over which summation takes place, is divided into rows and columns, as before. The transfer width and the adder width, however, must now be identical. The width can be chosen according to the criteria as outlined above. The columns of the matrix shaped summing unit are now completely disconnected, i.e. no transmission of carries takes place between the individual columns of the matrix during the process of summation. The carries occurring during the summation are collected in carry counters and processed at the end of the summation process.

Figure 17 shows the circuit of a "column" of the matrix shaped summing unit. The full "long accumulator" is spread over the various columns of the summing unit. The part allotted to one column is called "accu-memory", see (1) in Figure 17.5

To each cell of the accu-memory belongs a carry counter. The collection of carry counters of a column is called "carry-memory", see (2) in Figure 17. In these cells of the carry-memory all carries emerging from the adder/subtractor are collected and incorporated in the result at the very end of the summing process. The individual cells of the carry-memory must be so wide that they can take a carry (positive or negative) from each summand. For a vector length of 128 one needs, for example, 7 bits plus a sign bit resp. an 8 bit number in twos'-complement.

In Figure 17, for example, the column width is 32 bits and the width of the individual carry-memory cells is 16 bits. This allows a correct computation of sums with less than or equal to 32 K summands. The exponent identification (in Figure 17) has a width of e bit; consequently the column has 2<sup>e</sup> cells resp. the memory matrix 2<sup>e</sup> rows.

During the normal summation process the following happens:

- The mantissa section MANT, sign sg, and exponent identification EPI reach the input register RI, (3).

- In the next cycle

- the memory is addressed through EPI and the accu-part as well as the carry part are transferred to the corresponding section of the register before the sum-mation RBS, (4);

- the mantissa section, sg, and EPI are also transferred to the corresponding section of RBS, (5).

- 3. In the next cycle

- addition resp. subtraction according to sg is executed in the adder/subtracter (6). The result is transferred to the corresponding section of the register after the summation RAS, (7). According to the carry, the carrypart is adjusted in (8) by +1, -1 or not at

a rred to RAS, (9); EII is . ес to **RAS**, (10).

ie a

ddresses the memory, and

t ther with the carry-

In the  $\cdot$

sick into the memory. Since in er mantissa section s suppli ', be pipelined. This phases need to be be possible theremeans. active ... 1 fore, to r and to write i: the same of · f : memory during e 1 machine ry. ٧L is usual for register mean le

If in  $t \rightarrow -\infty$ .0. the same accu- and carry-memory ( ) condressed, the previously described processed any lead to a wrong result, since in the second sycle the result of the just started sure agreement we conflict. hould be read, which a typical pipeli e can be overcome by on a ari **duplic**ation mory several times which, have the vice.

Therefore, an

Therefore, an ier alternative. 'e suppose that the conse ive cycles manti: a sections was the grant exonent identification arrive. The state of the lowing two cases:

a) direct the state of the cher;

b) with not a conent dentification in bet-

the minarily often and mixed.

We first dear with case a).

and EPI of RBS con-The retailer EPI tain expense identification. The two are long ed in (... and in case of coincidencthe real proces from the memory to RBS is such soff in p t (13) of the selection on t (2.). Instea, the result of the addition of the first of the two consecutive summers is sheetly mansferred to RBS via there the side d summand can immedi-(14) s ately handen

Furthernore, (15) causes a dummy exponent to be read into ET of RAS. So, if in the same cycle a tarther third value with the same exponent identification is transferred to RI the case ENT/RI = EPI/RBS = EPI/RAS is avoided. The scase would a see a conflict in the select: | unit (12).

Thus, c secutive summends with the same exponent identification can be added without memory avolvement. The intermediate values may be written into the memory or discarded (stora blockade on). Only the last value written into the memory via RAS. must b

We now deal with case b).

b) Three values EPI<sub>1</sub>, EFI<sub>2</sub>, EPI<sub>3</sub> with EPI<sub>1</sub> = EPI<sub>3</sub> ≠ 1 PI<sub>2</sub>. In this case EPI/RI and EPI/RAScontain the same exponent identification. The two registers are compared in (16). In the following cycle the contents of RAS is directly transferred to RBS through part (17) of the selection unit (12). The read process from the memory is again suppressed in (13). The intermediate value may be written into the men ry. It can also be suppressed.

In this way, any consecutive mantissa sections can

The numbers enclosed in round parentheses in the text indicate in the corresponding Figure that part of the circuitry which is marked with the same number.

| зе | add   | ed | and   | the | С  | rries  | C | 11 | €. |

|----|-------|----|-------|-----|----|--------|---|----|----|

|    | ınteı |    |       |     |    |        |   |    |    |

| ₩e | now   | co | nside | r t | he | proces | S | οf | r  |

The central read central produc dresses so that the accumemor: least significant to the mas This sequence is a must lead to carry handling. The add: through the multiplexer () Wires (19), (20) for transier of from column to column. The carryare fed to the next more signific they are taken into the martiss: To get there the multiple er over. The carry, which is so re. plement for convenience, first into sign-magnitude-repre entat sary, expanded in length -2. the carry is added and to the lbit-carry (positive or 1 the unit for preparing th storage in RAS. The ab  $m \circ n$ there be stored either in bar t register or in a 2bit auxiliary

During the process of redelete the particular stop a circuitry part which is example, be done by writing rious scalar products resolated, the process of reach the computation of the frammands are continuously accuracy—memory.

From the most significant the memory is transferred register, (24) in Figure ry is transferred with a wire (20) to the least state available for the reassignificant row.

The final carry treatment resp. multi-stage pipeling ing carries are included of this part of the cirche result appear, the first.

In another part of the shown in Figure 18, the t cant digits must be for digit of the more signi: tains the result sign; s zero) means positiv , lar mal 9, hexadecimal 3) me ble to initialize both circuitry for filtering information now chacks the circuit whethe the not equal to the sign do higher significant regis case or if there is no s decimal system) at posit is enabled for the ctur to fill both regis ers rows. If, however, the abled in the previous cy abled for one cycle only

may therefore be doril

table with entries Trans

in the carry

g the result.

Intinuous adead from the ificant row.

The necessary the memory

carries lead s of a column column. There ction of RBS. is switched he twos'-comto he changed i, if necestructure cycle, a a possible ansferred to ter temporary d carry can he RAS-carry ter (23).

advisable to mmediately by This can, for to it. If vato be accumustarted until inished. The ed into the

g :

re:

ic

1 3 W

t

(

nc.

$\mathbf{di}_{1}$

carry part of kiliary carry me, this carthe cycle via dilumn to have s of the more

ins a singlestill remain-. At the end ady rows of ficant ones

6), which is the signifisignificant er (28) con-(preferably iual 1, deci-. t is advisith zero. The h significant presented to t one digit ored in the this is the g. 1..8 in a the transfer t clock cycle consecutive already enlist be reen-. circuit (29) llowing state er enable".

| State | output<br>sign<br>O | of<br>check<br>1 |  |

|-------|---------------------|------------------|--|

| 1     | 1/0                 | 2/1              |  |

| 2     | 1/1                 | 3/1              |  |

| 3     | 1/0                 | 3/1              |  |

The transfer into the registers ends if only rows with sign digits follow. Finally, in both registers those rows appear, which contain the mantissa of the floating-point result. One obtains the exponent from the position as well as from the initial address resp. from the number of cycles necessary for reading. Furthermore, the information required for the rounding is easily obtained during output. It serves for a possible adaptation of the result.

The circuitry shown in Figure 17 may be varied to reduce the number of input/output lines, e.g. by transferring the carry count (19) through the MANT inputs. The Figure is intended just to show principles, and not tricky details.

# 6. Systems with large Exponent Range and further Remarks

Many computers have a very modest exponent range. This is for instance the case for the system /370 architecture. If in the decimal system, for instance, l=17, el=-75 and e2=75 the full length L=k+2e2+2l+2 |e1| of the registers (see Figure 1 and Figure 2) can more or less easily be provided. Then sums and scalar products of the form (I) and (II) can be correctly computed for all possible combinations of the data by the technique discussed in this paper without ever getting an overflow or an interrupt.

However, there are also computers on the market with a very large exponent range of several hundred or thousand. In such a case it may be costly to provide the full register lengths of L=k+2e2+2l+2 |el| for the techniques discussed in this paper. It is most useful then to reduce the register lengths to the single exponent range and instead of L to choose  $L^*=k+e2+2l+|e1|$  or even a smaller range  $e'\le e\le e''$  with  $el\le e'$  and  $e''\le e2$  and correspondingly L'=k+e''+2l+|e'|.

Traditionally, sums and scalar products are computed in the single exponent range  $e1 \le e \le e2$ . If |e1| and e2 are relatively large most scalar products will be correctly computable within this range or even in  $e' \le e \le e''$ . Whenever, in this case, the exponent of a summand in a sum or scalar product computation exceeds this range  $e' \le e \le e''$  an overflow has to be signalled which may cause an interrupt.

In such a case the exponent range could be extended to a larger size on the negative or the positive side or even on both sides. We may very well assume that the necessity for such an extension of the exponent range occurs rather rarely. The supplementary register extensions, which are necessary for the techniques discussed in this paper, could then, for instance, be arranged in the main memory of the system and the summation within the

extended register part may then be executed in software. Such procedure would slow down the computation of scalar products in rather rare cases. But it still always will deliver the correct answer.

We further discuss a few slightly different methods how to execute accumulating addition/subtraction and the scalar product summation on processors with large exponent range.

On a more sophisticated processor the exponent range covered by the summing matrix could even be made adjustable to gain most out of this special hardware. This could be done by an automatic process of three stages:

- A special vector instruction analyzes the two vectors and computes the exponent range that covers most of the summands or products of the vector components. This step may be discarded if the best range is already known.

- The summing matrix gets properly adjusted to the range found in 1. and in a vector instruction the fitting part of the summand or products is accumulated into the summing matrix. If a summand or product does not fit into it it can be dealt by one of the two alternatives:

- a) Interrupt the accumulation and add that summand or product by software to the not covered extended parts of the accumulator which resides in main memory.

- b) Do not interrupt the accumulation, but discard this summand or product and mark this element in a vector flag register. Later the marked elements are added by software to the extended parts of the accumulator. This second way avoids interrupting and restarting the pipeline and will thus lead to higher performance than a).

- 3. In a final step the content of the summing matrix part of the accumulator is properly inserted between the extended parts to get the complete result in form of a correspondingly long variable in main memory.

Another cure of the overflow situation e  $\notin$  [e', e"] may be the following: Summands with an exponent e, which is less than e', are not added, but gathered on a "negative heap". Similarily summands with an exponent, which is greater than e", are gathered on a "positive heap". The negative and the positive heap may consist of a bit string or a vector flag register where each summand or vector component is represented by a bit. This bit is set zero if the summand was already added. It is set 1 if the component belongs to the corresponding heap. After a first summation pass over all summands the computed sum is stored. Then the positive and/or negative heap is shifted into te middle of the exponent range e'  $\leq$  e  $\leq$  e" by an exponent transformation and then added by the same procedure. After possibly several such steps the stored parts of the sum are put together and the final sum is computed. In many cases it will be possible to obtain the final result without summing up the negative heap.

Another possibility to obtain the correct result with a reduced register length L'=k+e'+2l+e'' is the following: The process of summation starts as usual. As soon as the exponent e of a

part is bui. ich rets the digit sequence of L' rv 1 ntissa of a normalized floatin 'im' e normalization, in if:. Then a "positive general, wil . a heap" is no "ce 7. And in most cases it will be pos n the correct rounded C result witho t possibly still necesg sary "negati et od computes all accumulating s ı 1 o icts correctly without consider aps as long as less eg. than e" - e' The negative heap can can only influensignificant digits of : 1€ L'. The reduction ful c mulator length L to a smaller siz , ma n e exponent under- or overflows in 1 . ion processes. This always makes · ent nling routine necessary. Whatever procedure represents a  $^{t_n}$  trdtrade off b. expenditure and runtime. A rather pri adling would consist in er a traditiona  $\circ \mathbf{r}$ the positive and negative heap. I. essage should be deli-15 vered to the ιt result is probably not precise. In the conte. n  $\gtrsim$  languages the accu- $\gtrsim$ " + 21 + e' represents g mulator of le = a new data t wh: le called <u>precise</u>. As i 1 e long as no e. Act the time or overflow occurs (e'  $\leq$  e  $\leq$  e") <u>ac</u> it.<u>on</u>  $\circ$  <u>f</u> les of type real, of products of  $\{\underline{1,\ldots}^{k} = \underline{r}^{k}\underline{i}\}$ as well as of scalar products of · v otc to a variable of this type can pr ated and it is error free. Accumu riables, products or scalar produ ble of type precise is associative. dependent of the order in which added. ъЭ, Vectorproces: the fastest computers which are pre alle. Their main field of -- i.Vc application sc. nti. ' computation. It should be natural .... v cte ressors compute vector operations correctly. a vector operations consist basically of the amponentwise addition and subtraction, the compositivise multiplication and the scalar product. The implementation of highly accurate vector addition subtraction and componentwise mul 'ic tic longs to the state of the art. The pu atime of accurate scalar proeal with a this paper. ducts has be Due to their .. h : see cr computation, vectorprocessors must, wever, also be able to support an automatic era Marrys 3 . sp. verification of the computed res in the order to achieve this it is necessary that all of liens, mentioned above, such as componentwise delition/subtraction, componentwise multiplication and scalar products can optionally be called with several roundings, in particular with the monotone downwardly directed rounding, the monotone wowardly directed rounding and the roun -; to the least including interval. We do not a uss the implementation of these roundings he It belongs to the state of the art. For furth a information we refer to the literature. Finally, we remark that the methods and procedures

outlined in the paper are also suitable to add up

sums of produces correctly which consist of more

than two factors, for example

rar

e', e"] an exponent

summand exce

$$\sum_{i=1}^{n} a_{i} + b_{i} *$$

# 7. Application to Multiple F and Arithmetic

We show in this chapter that ential parts of multiple precision rithm in easily be executed with high speed if a fig. calar product unit is available.

#### We consider

- 1. Double Precision Arithmeti

- 1.1 Sum and Difference

ble precision an be accumuectors or ma-

#### 1.2 Product

If a product a · b of tw doul sion factors a and b has to be complted, a actor can be represented as a sum of two sir ! recision numbers  $a = a_1 + a_2$  and  $b = b_1 + 1$ . ere a and b represent the first (higher sig i ant) l digits and a<sub>2</sub> and b<sub>2</sub> represent the 1 ower significant) l digits of a etc. The lication then requires the execution of a sc  $\mathbf{a} \cdot \mathbf{b} = (\mathbf{a}_1 + \mathbf{a}_2) = \frac{\mathbf{a} \cdot \mathbf{c}}{1} + \mathbf{b}$ duct:

$a_1b_1 + a_1b_2 + a_2b_1 \quad a_2b_2$  (1)

where each summand is doul poision. These can be added by the toronique desped in this paper.

Similarly, products of pre t factors can be computed. As in (1) products o double precision numbers are expressed b calar product of single precision : right hand side of (1) each san ċ is le precision number which can le resse sum of two single precision  $\mathbf{n}_0$   $\gg$  -s . In |t|f a product of four double precisi number leads to the following formulas, will are planatory.

$$a \cdot b \cdot c \cdot d = (a \cdot b) ( \cdot \cdot \cdot ) =$$

Thus a.b.c.d can be and a of 64 products of two singl or ::ion ach. The case of product. 20 C uble precision matrices is a li ∪ m∈ cult. But it can, in principle, b reat arily. If a product of two double ·isi s has to be No. computed the two matricarc rst presented as

sums of two single precision matrices. Multiplication of these sums then leads to a sum of products of single precision matrices:

$$a \cdot b = (a_1 + a_2) (b_1 + b_2) = a_1b_1 + a_1b_2 + a_2b_1 + a_2b_2$$

(2)

Each component of the products on the right hand side of (2) is computed as a scalar product. Thus each component of the product matrix a • b consists of a sum of scalar products which itself is a scalar product.

In case of matrix products, which consist of more than two double precision matrix factors, one has to take into account that the components of (2) may already be pretty long. They may consist of 10 or 20 consecutive digit sequences of single precision lengths. These sums of single precision matrices then have to be multiplied with other such sums, which leads to a sum of matrix products. Each component of this sum can be computed as a scalar product of single precision numbers.

#### 2.

Arithmetic of triple precision is a special case of quadruple precision arithmetic.

# 3. Quadruple Precision Arithmetic

# 3.1 Sum and Difference

Each summand of quadruple precision can be represented as a sum of two double precision summands. Thus sums of two or more quadruple precision summands can be added as expressed by the following formulas:

$$a + b = a_1 + a_2 + b_1 + b_2$$

$$\begin{array}{l} a + b + c + \dots + z = \\ a_1 + a_2 + b_1 + b_2 + c_1 + c_2 + \dots + z_1 + z_2 \end{array}.$$

Sums of quadruple precision vectors or matrices can be treated correspondingly.

## 3.2 Products

Each quadruple precision number can be represented as a sum of four single precision numbers  $a=a_1+a_2+a_3+a_4$ . Multiplication of such sums requires the execution of a scalar product:

$$a \cdot b = (a_1 + a_2 + a_3 + a_4) \cdot$$

$$(b_1 + b_2 + b_3 + b_4) = \sum_{i=1}^{4} \sum_{j=1}^{4} a_j \cdot b_j$$

(3)

Similarily, products of more than two quadruple precision factors can be computed. We indicate this process by the following formulas, which are self-explanatory.

a·b·c·d :

$$(a \cdot b) (c \cdot d) = \begin{pmatrix} 4 & 4 \\ \Sigma & \Sigma \\ i=1 & j=1 \end{pmatrix} a_i b_j \begin{pmatrix} 4 & 4 \\ \Sigma & \Sigma \\ i=1 & j=1 \end{pmatrix} c_i d_j =$$

<sup>&</sup>lt;sup>6</sup>High speed scientific puta. on usually done in the long data for De cision here means the double | . le. that format. If the usual long is a alled double precision our dans. · :i esponds to quadruple or exten (

$$= \begin{pmatrix} 32 & \mathbf{a^i} \\ \Sigma & \mathbf{a^i} \end{pmatrix} \begin{pmatrix} 32 & \mathbf{c^j} \\ \Sigma & \mathbf{c^j} \end{pmatrix} = \begin{pmatrix} 32 & 32 \\ \Sigma & \Sigma \\ \mathbf{i} = 1 & \mathbf{j} = 1 \end{pmatrix} \mathbf{a^i c^j} . \tag{4}$$

There the 16 double precision summands  $a_i^b_j$  and  $c_i^d_j$  of the two factors of (4) are each represented as sums of two single precision-numbers. This leads to the product of the two sums over 32 single precision numbers  $a^i$  resp.  $c^j$  in the next line.

If a product of two quadruple precision matrices is to be computed each factor is represented by a sum of four single precision floating-point matrices as in (3).

Multiplication of these sums leads to a sum of matrix products. Each component of these matrix products is computed as a scalar product. The sum of these scalar products is again a scalar product.

It was the intention of this section to demonstrate that with a fast accumulating addition/subtraction or scalar product unit a big step towards multiple precision arithmetic, even for product spaces, can be done.

## 8. <u>Literature</u>

- [1] U. Kulisch: Grundlagen des Numerischen Rechnens Mathematische Begründung der Rechnerarithmetik, Bibliographisches Institut, Mannheim 1976

- [2] U. Kulisch and W.L. Miranker: Computer Arithmetic in Teory and Practice, Academic Press 1981

- [3] U. Kulisch and W.L. Miranker: The Arithmetic of the Digital Computer: A New Approach, SIAM-Review, March 1986, pp. 1-40

- [4] IBM System /370 RPQ, High Accuracy Arithmetic, Publication Number SA 22-7093-0

- [5] High Accuracy Arithmetic, Subroutine Library, General Information Manual, IBM Program Number 5664-185

- [6] High Accuracy Arithmetic, Subroutine Library, Program Description and User's Guide, IBM Program Number 5664-185, Publication Number GC 33-6163

- [7] T. Teufel: 'Ein optimaler Gleitkommaprozessor, Dissertation, Universität Karlsruhe, 1984

- [8] G. Bohlender and T. Teufel: BAP-SC: A Decimal Floating-Point Processor for Optimal Arithmetic, tic, to appear in: Computer Arithmetic, Scientific Computing and Programming Languages (E. Kaucher, U. Kulisch, Ch. Ullrich, Eds), B.G. Teubner, 1987

- [9] Arithmos Benutzerhandbuch, SIEMENS AG., Bestell-Nr.: U 2900-J-Z 87-1

For a supplementary bibliography see the literature listed in [3].

Figure :: Transf reg ers and adders of different winth a, :: instance: t=4, a=6). The transf registers are represented without

Figure 8: Task of the shift unit

$\overline{\mathbf{m}}_1$  length of mantissa, number of digits of the mantissa  $h_1$  number of digits of a row of the summing matrix

Figure 9: Description of the shift process

Figure 10: Exponent identification of the sections of the transfer rows

Figure 11: Simplified adder selection by row identification  $y_i$

CY: carry with sign selection logic: add/subtr, if (selection-z) and (tag-z) or (selection-(z-1) and (tag-(z-1) add/subtr. zero else

Figure 12: Structure of a section of the matrix row y, for a m t

Pigure 15: Structure of a section with several adder / subtracters and transfer registers (for example 2a - 3t) in a simplified representation without tag-fields for exponent identification and control lines.

SL: selection