# A Design of Time-Optimum and Register-Number-Minimum Systolic Convolver

Hiroshi Umeo (†)

Osaka Electro-Communication University Neyagawashi, Hatsucho, 18-8, Osaka, 572, Japan

#### Abstract

We present an optimum bit-parallel/word-sequential systolic convolver. Our design is the best one among the previous many convolvers in the sense that its optimality in time and space performances is simultaneously attained without augmenting any global control, broadcasting, preloading, and/or multi sequential or parallel I/O ports, which were allowed in most of the previous designs. As an application of our convolver we give a systolic polynomial division in exactly n + O(1) steps on [min (n-m, m)/2] + O(1) systolic cells, for the division of any degree n polynomial by any degree m polynomial(n  $\geq$  m).

#### 1. Introduction

Convolution is probably one of the most important problems in the fields of signal and image processing. A large number of convolution algorithms have been proposed, since this type of computation is commonly used for many problems, such as pattern matching, digital filtering, discrete Fourier transforms, polynomial multiplication and division, and so on. Recently much attention has been paid to the study of systolic convolution algorithms[4-5], [7], [9-12], [14], [18-19], [21-24], [27-29], [33-36] and several practical constructions and implementations on VLSI are made[12], [18], [27], [35].

In this paper we will present a time-optimum and register-number-minimum systolic convolver. Our algorithm is based on Atrubin's binary parallel multiplier[2], Knuth's its revised version[20] and Cole's real-time iterative palindrome recognizer[8], which have been known as tricky cellular algorithms.

The systolic array that we assume is the most basic model which consists of a locally-connected semi-infinite array of identical systolic cells with a single I/O port being positioned at one end of the array. The data broadcasting, preloading, and/or multi sequential or parallel I/O ports are not allowed in our model.

It is shown that there exists a systolic array M which can compute the convolution  $c_i(i = 0, 1,$ 2, ...., n + m - 1) of any two finite sequences  $a_j$  (j = 0, 1, 2, ..., n - 1) and  $b_\ell$  ( $\ell$  = 0, 1, 2, ..., m - 1) in optimum real-time, exactly in n + m + O(1) steps, using  $[\min(m,n)/2] + O(1)$  systolic cells. The number of data registers in each systolic cell is minimum. A new data routing scheme developed for our convolver helps us to understand the correctness of the tricky algorithms above. As an application of our convolver, we give a systolic real-time pattern matcher and show that not only data preloading but also broadcasting are not necessarily essential operations in the design of systolic optimum-time pattern matcher. In addition we give a fastest systolic polynomial divider which can compute the polynomial division in exactly n + O(1) steps on [min(n-m, m)/2] + O(1)systolic cells, for the division of any degree n polynomial by any degree m polynomial  $(n \ge m)$ . The is time-optimum divider register-number-minimum. Our design is superior to the previous ones [21], [33], [36] in both the time and space(register-number) complexities.

The organization of this paper is as follows: In section 2 an optimum real-time and register-number-minimum systolic convolver is presented. Its validity is also given. In section 3 several variations and applications of our convolver are presented. Lastly we give a conclusion in section 4.

### Time-optimum and register-number-minimum systolic convolver

#### 2.1 Basic definitions

We first consider the convolution of two infinite sequences defined as follows: Convolution: Given two infinite sequences A and B such that

$$A = \langle a_0, a_1, \dots, a_i, \dots \rangle$$

$$B = \langle b_0, b_1, \dots, b_j, \dots \rangle$$

Compute an infinite sequence C,

$$c = \langle c_0, c_1, \dots, c_i, \dots \rangle, \dots (3)$$

defined by

$$c_i = \sum_{k=0}^{i} a_k b_{i-k}$$

,  $i = 0, 1, 2, \dots$  (4)

<sup>(†)</sup> The author stays as an Alexander-von-Humboldt researcher at Institut für Theoret. Informatik, Techn. Universität Braunschweig, Gaussstrasse 11, D-3300, Braunschweig, West Germany.

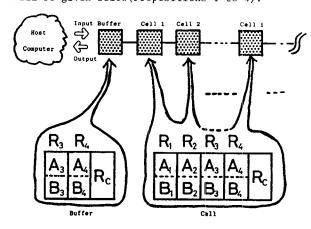

A systolic convolver M that we design consists of a buffer and a semi-infinite array of identical processors, called systolic cells,  $C_i$ , i = 1, 2, ...., that operate synchronously at discrete time steps drived by a common clock. See Fig. 1. The input  $(a_i, b_i)$ ,  $i = 0, 1, 2, \ldots$ , is fed serially to the leftmost cell via the buffer, and from which the serial output  $c_j$ ,  $j=0, 1, 2, \ldots$ , is also obtained. The buffer receives a pair of  $(a_i,$  $b_i$ ),  $i = 0, 1, 2, \ldots$ , at time t = i from the h one step. The buffer also outputs c, to the host computer at time t = j + k at the rate of one symbol one step, where k is some fixed integer, for any nonnegative integer j. We establish the following main theorem. The design of the convolver and its correctness will be given below(Propositions 1 to 4).

Fig.1 An illustration of real-time systolic convolver.

[Theorem 1] The systolic convolver M presented below can compute the convolution  $c_1$  (i = 0, 1, 2, ....) of two infinite sequences  $a_1$ ,  $b_2$  (j = 0, 1, 2, ....) in real-time, that is, for any i, i = 0, 1, 2, ...., M outputs  $c_1$  at time t = i + k, where k is some fixed integer. The number of data registers in each systolic cell is minimum. Further M outputs the convolution  $c_i$  ( $i = 0, 1, 2, \ldots, 2n - 1$ ) of  $a_i$ ,  $b_i$  ( $j = 0, 1, 2, \ldots, n - 1$ ) in exactly 2n + 0(1) steps, using [n/2] + 0(1) systolic cells.

# 2.2 Design

First we design a systolic convolver with each cell having four pairs of data registers, since it helps us to understand the correctness of our convolver. Afterward we will show that three-pair is the necessary and sufficient data-register number for the real-time convolution computation.

# Basic cell definition:

Each systolic cell has four pairs of data registers  $R_1$  ( $1 \le j \le 4$ ) and  $R_2$ . Each  $R_3$  consists of two subregisters  $R_4$  and  $R_3$ , storing ( $a_1^2$ ,  $b_2^2$ ) for some k. The buffer has three registers acting similarly as  $R_3$ ,  $R_4$  and  $R_4$  of the systolic cell. See Fig. 1. Each register is used for the following purposes:

${\bf R_1}$ ,  ${\bf R_2}$ : Data holding register.  ${\bf R_3}$ : A pipeline register which transmits data

to the right neighbour cell at unit speed.  $R_{\lambda}$ : Stores data temporary.

Stores the partial sum of convolution and transmits it to the left neighbour  $\mathbf{R}_{\mathbf{c}}$  at unit speed.

In the description below we use the following symbolic conventions.

$R_{i}(i)$ : Denotes the content of  $R_{i}$  in  $C_{i}$  at step t. Similar notations are used for other registers.  $R = \phi$ ,  $R \neq \phi$ ,  $R \leftarrow \phi$ : Each denotes that the register R is empty, is not empty, and is set empty, respectively.

#### ■ Parallel Data Routing Scheme:

• Initialization: At time

$$t=0$$

we assume that: Buffer:  $R_3^0(\text{buffer})=(a_0,b_0)$ ,  $R_4^0(\text{buffer})=\phi$

$$C_1(1\geq 1)\colon R_1^0(1)=\phi\;(1\leq j\leq 4) \qquad \qquad ......(5)$$

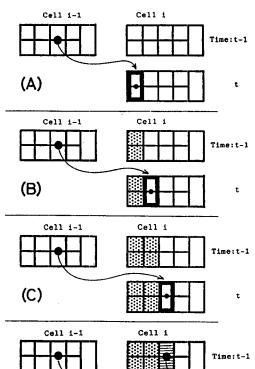

Fig. 2 Data routing scheme for real-time systolic convolver.

# Basic operations:

The operation of the systolic cell consists of data routing which involves  $R_j (1 \leq j \leq 4)$  and convolution computation on  $R_j$ . Both of them are performed simultaneously, however, we will explain them separately for ease of description and understanding.

In the equation(7) we regard  $R_3^{t-1}$  (i-1) as  $R_3^{t-1}$  (buffer) in the case i=1.  $C_1$  does nothing at time t while  $R_3^{t-1}$  (i-1) is empty. Let t be the time that  $R_3^{t-1}$  (i-1) has its first data. Then, within the next three steps, that is, t+1, t+2, and t+3,  $C_1$  performs the operation (A), (B), and (C) in this order. After that  $C_1^{t-1}$  follows (D) at every step. Each data-pair is transmitted through the pipeline register  $R_3^{t-1}$  in the right direction at unit speed until it will find an empty  $R_1^{t-1}$  and/or  $R_2^{t-1}$ . When they are found,  $R_1^{t-1}$  has a priority for storing the data. The next pair will be loaded in  $R_2^{t-1}$  in the same cell. Once a pair is stored in  $R_1^{t-1}$  or  $R_2^{t-1}$ , it will stay within that cell forever. The content of  $R_1^{t-1}$  is also copied by  $R_2^{t-1}$  in the same cell at the next step and is stored temporary in it. Fig. 2 shows our data routing scheme given above.

# ■ Computation rule for convolution:

•Initialization:

$$R_c^0$$

(buffer) =  $R_c^0$ (i) =  $\phi$ , for any  $i \ge 1$ . .....(8)

Out time

$$t(t \ge 1)$$

:

Buffer:  $R_C^{t}(\text{buffer}) + R_C^{t-1}(1)$  ......(9)

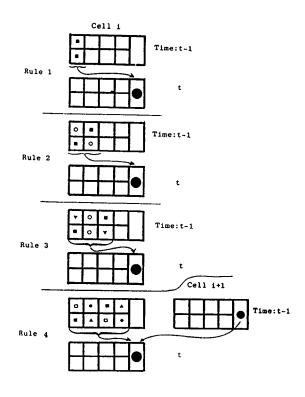

$C_1(i \ge 1)$ : Each cell  $C_1$  obeys the rule given below according to the number of pairs of data loaded in its  $R_1(1 \le j \le 4)$  at time  $t-1$ . We will refer them as rule 1, 2, 3, and 4, respectively.

$$\begin{aligned} & \text{WNo-pair:} & \quad \textbf{C}_4 & \text{does nothing for its } \textbf{R}_c & \text{at time t.} \\ & \text{Wone-pair:} & \quad \textbf{R}_c^{\text{t}}(1) + \textbf{A}_1^{\text{t}-1}(1) & \textbf{B}_1^{\text{t}-1}(1) \\ & \text{STwo-pair:} & \quad \textbf{R}_c^{\text{t}}(1) + \textbf{A}_1^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) + \textbf{A}_2^{\text{t}-1}(1) & \textbf{B}_1^{\text{t}-1}(1) \\ & \text{WThree-pair:} & \quad \textbf{R}_c^{\text{t}}(1) + \textbf{A}_1^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) + \textbf{A}_2^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) \\ & \quad + \textbf{A}_3^{\text{t}-1}(1) & \textbf{B}_1^{\text{t}-1}(1) & \textbf{B}_3^{\text{t}-1}(1) \\ & \quad + \textbf{A}_3^{\text{t}-1}(1) & \textbf{B}_1^{\text{t}-1}(1) & \textbf{B}_3^{\text{t}-1}(1) \\ & \quad + \textbf{A}_3^{\text{t}-1}(1) & \textbf{B}_1^{\text{t}-1}(1) & \textbf{A}_2^{\text{t}-1}(1) \\ & \quad + \textbf{A}_3^{\text{t}-1}(1) & \textbf{B}_1^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) \\ & \quad + \textbf{A}_4^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) \\ & \quad + \textbf{A}_4^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) \\ & \quad + \textbf{A}_4^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) \\ & \quad + \textbf{A}_4^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) \\ & \quad + \textbf{A}_4^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) \\ & \quad + \textbf{A}_4^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) \\ & \quad + \textbf{A}_4^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) \\ & \quad + \textbf{A}_4^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) \\ & \quad + \textbf{A}_4^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) \\ & \quad + \textbf{A}_4^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) \\ & \quad + \textbf{A}_4^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) & \textbf{B}_2^{\text{t}-1}(1) \\ & \quad + \textbf{A}_4^{\text{t}-1}(1) & \textbf{B}_4^{\text{t}-1}(1) & \textbf{B}_4^{\text{t}-1}(1) \\ & \quad + \textbf{A}_4^{\text{t}-1}(1) & \textbf{B}_4^{\text{t}-1}(1) & \textbf{B}_4^{\text{t}-1}(1) \\ & \quad + \textbf{A}_4^{\text{t}-1}(1) & \textbf{B}_4^{\text{t}-1}(1) & \textbf{B}_4^{\text{t}-1}(1) \\ & \quad + \textbf{A}_4^{\text{t}-1}(1) & \textbf{B}_4^{\text{t}-1}(1) & \textbf{B}_4^{\text{t}-1}(1) \\ & \quad + \textbf{A}_4^{\text{t}-1}(1) & \textbf{B}_4^{\text{t}-1}(1) & \textbf{B}_4^{\text{t}-1}(1) \\ & \quad + \textbf{A}_4^{\text{t}-1}(1) & \textbf{B}_4^{\text{t}-1}(1) & \textbf{B}_4^{\text{t}-1}(1) \\ & \quad + \textbf{A}_4^{\text{t}-1}(1) & \textbf{B}_4^{\text{t}-1}(1) & \textbf{B}_4^{\text{t}-1}(1) \\ & \quad + \textbf{A}_4^{\text{t}-1}(1) & \textbf{B}_4^{\text{t}-1}(1) & \textbf{B}_4^{\text{t}-1}(1) \\ & \quad + \textbf{A}_4^{\text{t}-1}(1) & \textbf{B}_4^{\text{t}-1}(1) &$$

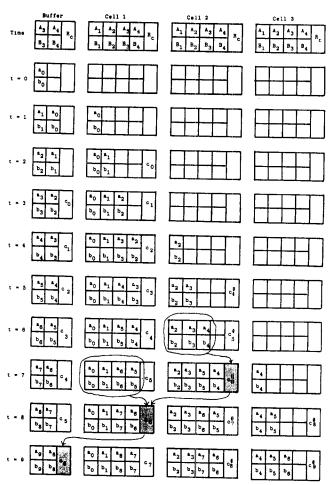

Fig. 3 shows our computation rule for convolution. Exactly the following equations hold for R in the buffer and C  $(i \geq 1)$ . Consult Fig. 4 for the help of understanding of these equations. The mark @ in R denotes that its content is partial.

$$R_{c}^{t}(buffer) = \begin{cases} \phi & (t < 3) \\ c_{t-3} & (t \ge 3) \end{cases}$$

$$R_{c}^{c}(1) = \begin{cases} \phi & (t < 2) \\ c_{t-2} & (t \ge 2) \end{cases}$$

$$R_{c}^{t}(1) = \begin{cases} \phi & (t < 3i - 1, i \ge 2) \\ c_{t+i-3} & (t \ge 3i - 1, i \ge 2) \end{cases}$$

$$(13)$$

## 2.3 Validity

We will show informally the correctness of our convolver. Let  $\mathbf{c_4}$  be the term such that:

$$c_{i} = a_{i}b_{0} + a_{i-1}b_{1} + \dots + a_{1}b_{i-1} + a_{0}b_{i}$$

defined in (4). The index i can be represented as  $i = 4k + \ell$ , where k is any nonnegative integer and  $\ell$  is any integer in  $\{0, 1, 2, 3\}$ . Then,

$$c_i = c_{4k+\ell} = w_1 + w_2 + \dots + w_k + w_{k+1} + \dots (14),$$

Fig.3 Computation rules for convolution.

where  $w_1, w_2, \dots, w_{k+1}$  are defined as follows:

$$w_{j} = a_{1-(2j-2)} b_{2j-2} + a_{1-(2j-1)} b_{2j-1} + a_{2j-2} b_{1-(2j-2)} + a_{2j-1} b_{1-(2j-1)}, 1 \le j \le k \text{ and}$$

$$w_{k+1} = \begin{cases} a_{2k}b_{2k} & \text{, when } \ell = 0 \\ a_{2k}b_{2k+1} + a_{2k+1}b_{2k} & \ell = 1 \end{cases}$$

$$a_{2k}b_{2k+2} + a_{2k+1}b_{2k+1} + a_{2k+2}b_{2k} & \ell = 2 \end{cases}$$

$$a_{2k}b_{2k+2} + a_{2k+1}b_{2k+1} + a_{2k+2}b_{2k} & \ell = 2 \end{cases}$$

The computation of the value  $c_{4k+k}$  is made on M as follows: The systolic cell  $c_{k+1}$  firstly computes  $w_{k+1}$ , using rule 1, 2, 3, or 4 depending on whether  $\ell=0$ , 1, 2, or 3, respectively. At the next step this partial sum is transmitted to the left neighbour cell  $c_k$  and  $w_k+w_{k+1}$  is computed on it, using rule 4. And at the next step, applying rule 4,  $c_{k-1}$  computes  $w_{k-1}+w_k+w_{k+1}$ , and so on. And k steps later,  $w_1+w_2+\dots+w_k+w_{k+1}$  is obtained on  $c_1$ . On the next step this value is

We wered by the buffer. See Fig. 4. Exactly the buckering proposition holds. We omit its proof.

[Proposition 1] For any nonnegative integer x in  $\{0, 1, 2, \ldots, k\}$ ,

$$R_c^{3k+\ell+2+x}(k+1-x) = W_{k+1} + W_k + \dots + W_{k-x+1}.$$

By letting  $\mathbf{x} = \mathbf{k}$  in [Proposition 1], we get the following equation:

$$R_c^{4k+\ell+2}(1) = W_{k+1} + W_k + \dots + W_1 = W_{4k+\ell}.$$

Thus, for any i, i = 0, 1, 2, ..., c, is obtained at the buffer at time t = i + 3 in real-time. The computation of  $c_{k+1}$  is started on  $c_{k+1}$  and uses  $c_k$ ,  $c_{k-1}$ , ...,  $c_1$  (k cells). So the systolic real-time convolver M uses [n/2] + 0(1) systolic cells for the computation of convolution  $c_1$  (i = 0, 1, 2, ..., 2n-1) of  $a_j$ ,  $b_j$  (j = 0, 1, 2, ..., n-1).

Fig.4 Snapshots of our real-time systolic

convolver of two infinite sequences(t=0 to

9).

## 2.4 Optimality

In this section it is shown that our systolic convolver M is optimum not only in the parallel time complexity but also in the number of registers  $\frac{1}{2}$

of each systolic cell. From the definition of I/O rates the time optimality in [Theorem 1] is easily seen. Next we show that three pairs of data registers in each cell 1, excluding R , are minimum for the real-time systolic computation of convolution.

[Proposition 2] The three pairs of data registers  $\mathbf{R}_1$ ,  $\mathbf{R}_2$ , and  $\mathbf{R}_3$  in each cell are necessary and sufficient for any real-time systolic convolver.

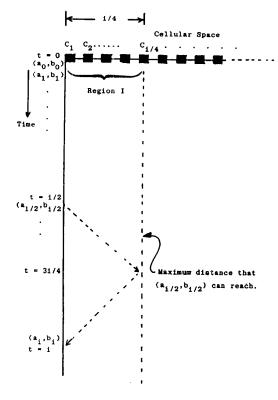

(Proof) Let  $c_i = a_i b_0 + a_{i-1} b_1 + \dots + a_1 b_{i-1} b_1 + a_0 b_i$ . We refer the set of cells  $c_1$ ,  $c_2$ , ...,  $c_{i/4}$  of M as region I. See Fig. 5. The following observations are obtained.

Fig. 5 A region of systolic cells which involve the computation of  $c_i = a_i b_0 + a_{i-1} b_1 + \dots + a_0 b_1$ .

- (1) It is the subterm  $a_1/2$   $b_1/2$  that can be computed firstly on M within 1+1 subterms which constitute  $c_1$ , since it is the first subterm that both of the input data are ready for the computation. Moreover the multiplication of  $a_1/2$  must be made on some cell in the region  $a_1/2$  since the pair is fed at time  $a_1/2$  and the result must be output at time  $a_1/2$  in real-time. From the same reason  $a_1/2$ ,  $a_$

- (2) The 1/4 pairs of data fed from time t = 3i/4 to i cannot go out of the region I, even if they march in the right direction at its maximum speed.

Therefore M must hold 3i/4(=i/2+i/4) pairs of input data on the region I consisting of i/4

systolic cells. So three pairs of data registers are necessary for our computation.

By a slight observation we show that the register R $_{4}$  of each systolic cell can be removed from M. The R $_{4}$  is used only for the rule 4. When we apply the rule 4, the following register R is used instead of R $_{4}^{-1}$ (i).

$$R = \left\{ \begin{array}{l} R_1^{t-1}(i+1) \text{, when } R_2^{t-1}(i+1) = \emptyset \text{,} \\ R_2^{t-1}(i+1) \text{, when } R_2^{t-1}(i+1) \neq \emptyset \text{ and } R_3^{t-1}(i+1) = \emptyset \text{,} \\ R_3^{t-1}(i+1) \text{, otherwise.} \end{array} \right.$$

It is easily seen from (7) that the content of  $R_4$  (i) is the same as that of R above.

## 3. Other convolvers and their applications

We will develop several variations and applications of our systolic real-time convolver designed in the preceding section. A slight modification enables us to use M for the computation of the convolution of one finite and one infinite sequences, which is an important problem in the fields of digital filtering.

[Theorem 2] The systolic convolver M can compute the convolution  $c_i$  ( $i=0,1,2,\ldots$ ) of an infinite sequence  $a_i$  ( $j=0,1,2,\ldots$ ) and a finite sequence  $b_0$  ( $k=0,1,2,\ldots$ , k-1) in real-time, using only  $\lfloor k/2 \rfloor + 0$ (1) systolic cells.

(Proof sketch) We use \* as an end mark of the finite sequence b, l = 0, i, 2, ..., k - 1. The input to M is  $(a_1, k)$  for any  $j \ge k$ . The number of systolic cells necessary for the computation is  $\lfloor k/2 \rfloor + O(1)$ , since the product of \* and a is zero.

If multiplication and addition operations are interpreted as character-comparison and boolean AND, respectively, then the convolution considered

above becomes the pattern matching problem[13], [15], [22]. In [22] and [29], were presented systolic pattern matching algorithms with global data broadcasting and/or preloading. In the next theorem it is shown that the both broadcasting and preloading are not necessarily essential operations in the design of real-time systolic pattern matcher.

[Theorem 3] For any infinite long "pattern" and any "text" of length k, the systolic convolver M can detect and output the positions of all occurrences of the text in the pattern in real-time, using  $\lfloor k/2 \rfloor + O(1)$  systolic cells.

The following theorem for open convolutions of two finite sequences is easily obtained from Theorems 1 and 2.

[Theorem 4] The systolic convolver M can compute the convolution  $c_1$  ( $i=0,1,2,\ldots,n+m-1$ ) of any two finite sequences  $a_1$  ( $j=0,1,2,\ldots,n-1$ ) and  $b_{\ell}$  ( $\ell=0,1,2,\ldots,m-1$ ) in exactly n+m+0(1) steps, using  $[\min(m,n)/2]+0$ (1) systolic cells.

Lastly we apply our convolver to the design of systolic real-time polynomial divider. Our design is superior to the previous ones[21], [33], and [36] in both the time and space complexities. In Table 1 we give a summary of the designs. Let's begin with the definitions. Let A(x) and B(x) be any polynomials of degree n and  $m(n \ge m)$ , respectively, such that:

$$A(x) = a_0 x^n + a_1 x^{n-1} + \dots + a_{n-1} x + a_n \dots (15),$$

$$B(x) = b_0 x^m + b_1 x^{m-1} + \dots + b_{m-1} x + b_m \dots (16).$$

Then there exist unique polynomials C(x) and D(x) that satisfy the following division property:

| Design                                    | Number of<br>Systolic Cells | Time<br>Complexity<br>(cycles) | I/O Rates     | 1/O Architecture                |                                                  |

|-------------------------------------------|-----------------------------|--------------------------------|---------------|---------------------------------|--------------------------------------------------|

| Kung[21]<br>(1982)                        | TÈ .                        | 2n + m                         | l-data/2-step | Sequential I/O at opposite ends | → <del>8 8 8</del> 8\$                           |

| Wada, Mizun<br>and Kawaguci<br>[33](1985) |                             | 2n + 2                         | l-data/l-step | Sequential I/O at opposite ends | <b>→8-6-8</b> ···· · <b>8</b> →                  |

| Zak and<br>Hwang[36]<br>(1985)            | n - m + 1                   | 2n - m + 2                     | l-data/l-step | Parallel I/O                    | <b>→</b> #-##→                                   |

| this paper                                | [min(n - m, m)/2]           | n<br>(optimum)                 | l-data/l-step | Sequential I/O at one end       | <del>*************************************</del> |

Table 1 Performance comparison of systolic polynomial divider in the case where degree n polynomial is divided by degree m polynomial.

$$\mathbf{z_0}^{\mathbf{n-m}} + c_1 \mathbf{x}^{\mathbf{n-m-1}} + \dots + c_{n-m-1} \mathbf{x}$$

$$\mathbf{z_0}^{\mathbf{n-m}} + c_1 \mathbf{x}^{\mathbf{n-m-1}} + \dots + c_{n-m-1} \mathbf{x}$$

$$\mathbf{z_0}^{\mathbf{n-m}} + c_1 \mathbf{x}^{\mathbf{n-m-1}} + \dots + c_{n-m-1} \mathbf{x}$$

$$\mathbf{z_0}^{\mathbf{n-m}} + c_1 \mathbf{x}^{\mathbf{n-m-1}} + \dots + c_{n-m-1} \mathbf{x}$$

$$\mathbf{z_0}^{\mathbf{n-m}} + c_1 \mathbf{x}^{\mathbf{n-m-1}} + \dots + c_{n-m-1} \mathbf{x}$$

$$\cdots (18)$$

Let  $\mathbf{z}_1$  (i = 0, 1, 2, ..., n+1) be the convolution of  $(\mathbf{b}_0, \mathbf{b}_1, \ldots, \mathbf{b}_m)$  and  $(\mathbf{c}_0, \mathbf{c}_1, \ldots, \mathbf{c}_{n-m})$ . Then the following equation holds.

Therefore coefficients of  $C(\mathbf{x})$  and  $D(\mathbf{x})$  are determined by the following equations:

$$c_{i} = \{ a_{i} - (b_{i}c_{0} + b_{i-1}c_{1} + \dots + b_{1}c_{i-1}) \}$$

$$/ b_{0}, 0 \le i \le n - m. \qquad \dots (21)$$

$$d_{j} = a_{i+n-m+1} - \sum_{j=0}^{n-m} b_{i+n-m+1-j}c_{j},$$

$$0 \le i \le m - 1. \qquad \dots (22)$$

#

Fig.6 Systolic cell  $\mathbf{C}_1$  for the polynomial divider.

We want to design a real-time systolic polynomial divider A which outputs both c (0  $\leq$  i  $\leq$  n - m) and d, (0  $\leq$  j  $\leq$  m - l) in exactly n + O(1) steps, when coefficients of A(x) and B(x) are given as inputs of A. The operation of A is based on M which computes the open convolution of (b\_0, b\_1, ...., b\_m) and (c\_0, c\_1, ....., c\_n\_m) in [Theorem 4]. Therefore the number of systolic cells needed for the division is [min(n - m + 1, m + 1)/2] + O(1) = [min(n - m, m)/2] + O(1). All of the systolic cells of A, except C\_1, are the same as these of M. So in the below, we will only give the description of C\_1.

these of M. So in the below, we will only serve the description of C<sub>1</sub>.

The cell C<sub>1</sub> consists of several registers shown in Fig. 6. The R<sub>0</sub> and S registers are added to the previous design. The R<sub>0</sub> is the data register storing a<sub>1</sub> ( $0 \le i \le n-1$ ), and b<sub>0</sub>, respectively. The S register assumes either "q" or "r" state, which notifies C<sub>1</sub> that the current computation is for the quotient or the remainder, respectively. From time t = 0 to n - m + 1, S assumes "q" and after that, from t = n - m + 2 to the end, S assumes "r". The change of the state in S is caused by the signal fed by the host computer at time t = n - m + 1. C<sub>1</sub> performs the operation given in Table 2 depending on whether S is "q" or "r", respectively.

In Fig. 7 we show an example of the systolic polynomial division on A in the case where n=7 and m=3. We give the following theorem without proof.

[Theorem 5] For the division of any degree n polynomial by any degree m polynomial (n  $\geq$  m), there exists a systolic array A which can compute the polynomial division in exactly n + O(1) steps on [min(n-m, m)/2] + O(1) systolic cells. The divider A is time-optimum and register-number-minimum.

#### 4. Conclusion

In this work we have presented a best systolic convolver which can compute the convolution c (i = 0, 1, 2, ...., n + m - 1) of any two finite sequences a (j = 0, 1, 2, ..., n - 1) and b\_{\varrho}( $\ell$  = 0, 1, 2, ..., m^j-1) in optimum real-time, exactly in n + m + O(1) steps, using  $[\min(m,n)/2]$  + O(1) systolic cells. The number of data registers in each systolic cell is minimum. Several variations and applications of our convolver, such as real-time pattern matcher and time-optimum polynomial divider, are also developed. Our convolver design is the best one as far as the design is within the systolic architectures.

#### Acknowledgement

The author is pleased to acknowledge the considerable assistance of Prof. Dr. R. Vollmar. This research is supported in part by an Alexander-von-Humboldt Foundation Fellowship and by the Grant-in-Aid(No.61750346) for Scientific Research of the Ministry of Education, Culture and Science of Japan.

#### References

[1] Apostolico, A. and Negro, A.; "Systolic algorithms for string manipulations", IEEE Trans. on Computers, Vol. C-33, No. 4, pp.361-364, (1984). [2] Atrubin, A.J.; "A one-dimensional real-time iterative multiplier", IEEE Trans. on EC., EC-14, pp.394-399, (1965).

[3] Baudet, G.M., Preparata, F.P., and Vuillemin, J.E.; "Area-time optimal VLSI circuits for convolution", IEEE Trans. on Computers, Vol. C-32, No. 7, pp.684-688, (1983).

[4] Cappello, P.R. and Steiglitz, K.; "Unifying VLSI array designs with geometric transformations", Proc. of the IEEE Intern. Conf. on Parallel Processing, pp.448-457, (1983).

[5] Cappello, P.R. and Steiglitz, K.; "Unifying VLSI array design with linear transformations of space-time", in "Advances in Computing Resaerch", Vol. 2, pp.23-65, JAI Press, (1984).

[6] Chen, I-Ngo and Willoner, R.;"An O(n) parallel multiplier with bit-sequential input and output", IEEE Trans. on Computers, Vol. C-28, No.10, pp.721-727, (1979).

[7] Cohen, D.; "Mathematical approach to iterative computation network", Proc. of The Computer Architecture, pp. 226-239, (1978).

[8] Cole, S.N.; "Real-time computation by n-dimensional iterative arrays of finite state machines", IEEE Trans. on Computers, Vol.C-18, No.4, pp.349-365, (1969).

[9] Culik II, K. and Fris, I.; "Topological transformations as a tool in the design of systolic networks", Tech. Rep of Waterloo Univ., CS-84-11, (1984).

[10] Danielsson, P.E.; "Serial/parallel convolvers", IEEE Trans. on Computers, Vol. C-33, No. 7, pp.652-667, (1984).

[11] Ersoy O.; "Semisystolic array implementation of circular class of the convolution of the convolution

circular, skew circular, and linear convolutions", IEEE Trans. on Computers, Vol. C-34, No. 2, pp.190-196, (1985).

[12] Evans, R.A., Wood, D., Wood, K., McCanny, J.V., McWhirter, J.G., and McCabe, A.P.H.;"A CMOS implementation of a systolic multi-bit convolver chip", in "VLSI 83( eds. F. Anceau and E.J. Aus)", pp.227-235, NorthHolland, (1983).

[13] Fisher, M.J. and Paterson, M.S.;"String-matching and other products",

$\begin{array}{lll} t = 0: & R_{j}^{0}(1) = R_{c}^{0}(1) = \phi, \ (0 \leq j \leq 4), \ \text{and} \ S^{0} = q \\ t = 1: & R_{0}^{1}(1) = (a_{0}, b_{0}), \ R_{j}^{1}(1) = R_{c}^{1}(1) = \phi, \ (1 \leq j \leq 4), \ \text{and} \ S^{0} = q \\ t \geq 2: & \text{Given below.} \end{array}$

```

\begin{array}{c} \underline{\text{while }} (S^{t-1} = "q" ) \text{ do } \{ A_0^t(1) + A_3^{t-1}(\text{buffer}); B_0^t(1) + B_0^{t-1}(1); \\ \underline{\text{if }} (R_1^{t-1}(1) = \phi ) \underline{\text{then }} \{ A_1^t(1) + \chi \ ; B_1^t(1) + B_3^{t-1}(\text{buffer}); R_c^t(1) + \chi \} \\ \underline{\text{else }} \underline{\text{if }} (R_2^{t-1}(1) = \phi ) \underline{\text{then }} \{ A_2^t(1) + \chi \ ; B_2^t(1) + B_3^{t-1}(\text{buffer}); R_c^t(1) + \chi \ \} \\ \underline{\text{else }} \underline{\text{if }} (R_3^{t-1}(1) = \phi ) \underline{\text{then }} \{ A_3^t(1) + \chi \chi \chi \ ; B_3^t(1) + B_3^{t-1}(\text{buffer}); R_c^t(1) + \chi \chi \chi \ \} \\ \underline{\text{else }} \underline{\text{if }} (R_4^{t-1}(1) = \phi ) \underline{\text{then }} \{ A_3^t(1) + \chi \chi \chi \chi \ ; B_3^t(1) + B_3^{t-1}(\text{buffer}); R_c^t(1) + \chi \chi \chi \chi \ \} \\ \underline{\text{else }} \underline{\text{if }} (R_4^{t-1}(1) = \phi ) \underline{\text{then }} \{ A_3^t(1) + \chi \chi \chi \chi \ ; B_3^t(1) + B_3^{t-1}(\text{buffer}); R_c^t(1) + \chi \chi \chi \chi \chi \ \} \\ \underline{\text{else }} \underline{\text{if }} (R_4^{t-1}(1) = \phi ) \underline{\text{then }} \{ A_3^t(1) + \chi \chi \chi \chi \chi \ ; B_3^t(1) + B_3^{t-1}(\text{buffer}); R_c^t(1) + \chi \chi \chi \chi \chi \ \} \\ \underline{\text{else }} \underline{\text{if }} (R_4^{t-1}(1) = \phi ) \underline{\text{then }} \{ A_3^t(1) + \chi \chi \chi \chi \chi \ ; B_3^t(1) + B_3^{t-1}(\text{buffer}); R_c^t(1) + \chi \chi \chi \chi \chi \ \} \\ \underline{\text{else }} \underline{\text{if }} (R_4^{t-1}(1) + A_3^{t-1}(1) \} \\ \underline{\text{else }} \underline{\text{if }} (R_4^{t-1}(1) + A_3^{t-1}(1) \} \\ \underline{\text{else }} \underline{\text{if }} (R_4^{t-1}(1) + A_3^{t-1}(1) \} \\ \underline{\text{else }} \underline{\text{if }} (R_4^{t-1}(1) + A_3^{t-1}(1) \} \\ \underline{\text{else }} \underline{\text{if }} (R_4^{t-1}(1) + A_3^{t-1}(1) \} \\ \underline{\text{else }} \underline{\text{if }} (R_4^{t-1}(1) + A_3^{t-1}(1) \} \\ \underline{\text{else }} \underline{\text{if }} (R_4^{t-1}(1) + A_3^{t-1}(1) \} \\ \underline{\text{else }} \underline{\text{if }} (R_4^{t-1}(1) + A_3^{t-1}(1) \} \\ \underline{\text{else }} \underline{\text{if }} (R_4^{t-1}(1) + A_3^{t-1}(1) + A_3^{t-1}(1) ) \\ \underline{\text{if }} (R_4^{t-1}(1) + A_3^{t-1}(1) + A_4^{t-1}(1) ) \\ \underline{\text{if }} (R_4^{t-1}(1) + A_3^{t-1}(1) + A_4^{t-1}(1) ) \\ \underline{\text{if }} (R_4^{t-1}(1) + R_4^{t-1}(1) )

```

Table 2 Operation of  $C_1$  of the real-time systolic polynomial divider.

SIAM-AMS, Proceedings, Vol.7, pp.113-125, (1974) [14] Foster, M.J. and Kung, H.T.; "The design of special purpose VLSI chips", IEEE Computer, Vol. 13, No. 1, pp.26-40, (1980).

[15] Galil, Z.; "Real-time algorithms string-matching and palindrome recognition", Proc. of the 8th ACM Symp. on Theory of Computing, pp.161-173, (1976).

[16] Gnanasekaran, R.;"On a bit-serial input and bit-serial output multiplier", IEEE Trans. on Computers, Vol. C-32, No. 9, pp.878-880, (1983).

[17] Gnanasekaran, R.;"A fast serial-parallel binary multiplier", IEEE Trans. on Computers, Vol.

C-34, No. 8, pp.741-744, (1985).

[18] Hurson, A.R. and Shirazi, B.;"A systolic multiplier unit and its VLSI design", Proc. of Computer Architecture, pp.302-309, (1985).

|                 | Buffer  A <sub>3</sub> A <sub>4</sub> R <sub>c</sub> B <sub>3</sub> B <sub>4</sub> | Cell 1  Ao A1 A2 A3 A4 S  Bo B1 B2 B3 B4 Rc                                                                    | Cell 2  A <sub>1</sub> A <sub>2</sub> A <sub>3</sub> A <sub>4</sub> B <sub>1</sub> B <sub>2</sub> B <sub>3</sub> B <sub>4</sub> R <sub>c</sub> | Cell 3  A <sub>1</sub> A <sub>2</sub> A <sub>3</sub> A <sub>4</sub> B <sub>1</sub> B <sub>2</sub> B <sub>3</sub> B <sub>4</sub> |

|-----------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| t = 0           | p <sup>0</sup>                                                                     | q.                                                                                                             | 0                                                                                                                                              |                                                                                                                                 |

| t - 1           | a <sub>1</sub> a <sub>0</sub> b <sub>1</sub> b <sub>0</sub>                        | ь <sub>0</sub>                                                                                                 | 0                                                                                                                                              | 0                                                                                                                               |

| t • 2           | b <sub>2</sub> b <sub>1</sub>                                                      | b <sub>0</sub> b <sub>1</sub> q                                                                                | 0                                                                                                                                              | 0                                                                                                                               |

| t = 3           | b <sub>3</sub> b <sub>2</sub>                                                      | b <sub>0</sub> b <sub>1</sub> b <sub>2</sub> c <sub>1</sub>                                                    | 0                                                                                                                                              | 0                                                                                                                               |

| τ = 4           | * b <sub>3</sub> c <sub>1</sub>                                                    | a3         c0         c1         c2         q           b0         b1         b2         b3         c2         | 0                                                                                                                                              | 0                                                                                                                               |

| Signal<br>t = 5 | * 5 * 4 ° 2                                                                        | a4     c0     c1     c3     c2     q       b0     b1     b2     *     b3     c3                                | b <sub>3</sub> 0                                                                                                                               | 0                                                                                                                               |

| t = 6           | *6 *5 c3                                                                           | b <sub>0</sub> b <sub>1</sub> b <sub>2</sub> * * c <sub>4</sub>                                                | b <sub>3</sub> , d <sub>0</sub>                                                                                                                |                                                                                                                                 |

| t = 7           | *7 *6 c4                                                                           | b <sub>0</sub> b <sub>1</sub> b <sub>2</sub> • c <sub>4</sub> r d <sub>0</sub>                                 | c <sub>2</sub> c <sub>3</sub> c <sub>4</sub> d <sub>1</sub> b <sub>3</sub> • • d <sub>1</sub>                                                  | 0                                                                                                                               |

| t - 8           | • • • • • • • • • • • • • • • • • • • •                                            | b <sub>0</sub> b <sub>1</sub> b <sub>2</sub> • • d <sub>1</sub>                                                | c <sub>2</sub> c <sub>3</sub> · · · c <sub>4</sub> d <sub>2</sub> b <sub>3</sub> · · · ·                                                       | •                                                                                                                               |

| τ - 9           | d <sub>1</sub>                                                                     | c <sub>0</sub> c <sub>1</sub> **     *       b <sub>0</sub> b <sub>1</sub> b <sub>2</sub> *     d <sub>2</sub> | HHI                                                                                                                                            |                                                                                                                                 |

| t = 10          | d <sub>2</sub>                                                                     |                                                                                                                |                                                                                                                                                |                                                                                                                                 |

Fig. 7 Snapshots of the real-time systolic polynomial divider( t = 0 to 10 ).

[19] Ibarra, O.H., Kim, S.M., and Palis, M.A.; "Designing algorithms using systolic sequential machines", IEEE Trans. on Computers, Vol. C-35, No. 6, pp.531-542, (1986). [20] Knuth, D.E.; "The Art of Computer Programming",

Vol.2, pp297-299, Second Edition, (1980).

[21] Kung, H.T.; "Use of VLSI in algebraic computation: Some suggestions", Proc. of 1981 ACM Symp. on Symbolic and Algebraic Computation, pp.218-222, (1981).

[22] Kung, H.T.; "Why systolic architecture", IEEE Computer, Jan., pp.37-46, (1982).

[23] Leiserson, C.E. and Saxe, J.E.; "Optimizing synchronous systems", J. of VLSI and Computer Systems, Vol.1, No.1, pp.41-67, (1983).

[24] Li, Guo-Jie and Wah, B.W.; "The design of optimal systolic arrays", IEEE Trans. on Computers,

Vol. C-34, No. 1, pp.66-77, (1985). [25] Luk, W.K. and Vuillemin J.E.; "Recursive implementation of optimal time VLSI integer multipliers", Tech. Rep. of Carnegie-Mellon Univ., CMU-CS-84-149, (1984).

[26] Lyon, R.F.; "Two's complement pipeline multiplier", IEEE Trans. on Communications, Comm-24, pp.418-425, (1976).

[27] McWhirter, J.G. and McCanny, J.V.; "Novel multibit convolver/correlator chip design based on systolic array principles", Proc. of SPIE, Vol. 341, Real Time Processing V(1982), pp.66-73, (1982).

[28] McWhirter, J.G., Wood, D., Wood, K.W., Evans, R.A., McCanny, J.V., and Mccabe A.P.H.; "Multibit convolution using a bit level systolic array", IEEE Trans. on Circuits and Systems, Vol. CAS-32, No. 1, pp.95-99, (1985).

[29] Mukhopadhyay, A.; "Hardware algorithms for nonnumeric computation", IEEE Trans. on Computers, Vol. C-28, No. 6, pp.384-394, (1979).

[30] Preparata, F.P.;"A mesh-connected area-time optimal VLSI multiplier of large integers", IEEE Trans. on Computers, Vol. C-32, No. 2, pp.194-198, (1983).

[31] Ullman, J.D.; "Computational Aspects of VLSI",

Computer Science Press, p.495, (1984).

[32] Umeo, H.; "A class of SIMD algorithms implemented on systolic VLSI arrays", IEEE Proc. of the Inter. Conf. on Parallel Processing,

Implemented on systolic VLSI arrays", IEEE Proc. of the Inter. Conf. on Parallel Processing, pp.374-376, (1984). [33] Wada, k., Mizuno, M., and Kawaguchi, K.;"Systolic algorithms for polynomial multiplication and division", Tech. Rep of IECE(Japan), AL84-60, pp.97-106, (in Japanese), (1985).

[194] Wang, Chin-Liang, Wei, Che-Ho, and Chen Sin-Horng; Improved systolic array for linear discriminant function classifier", Electronics Letters, 16th Jan., Vol. 22, No. 2, pp.85-86, (1986).

[35] Wood, D., Evans, R.A., and Wood, K.W.; "An 8 bit serial convolver chip on a bit level systolic array", Proc. of the Custom Integrated Circuits

Conf., pp.256-261, (1983).

[36] Zak, S.H. and Hwang, K.; "Polynomial division on systolic arrays", IEEE Trans on Computers, Vol. C-34, No. 6, pp.577-578, (1985).